# CPU. Register Set

#### Registers set of 18086

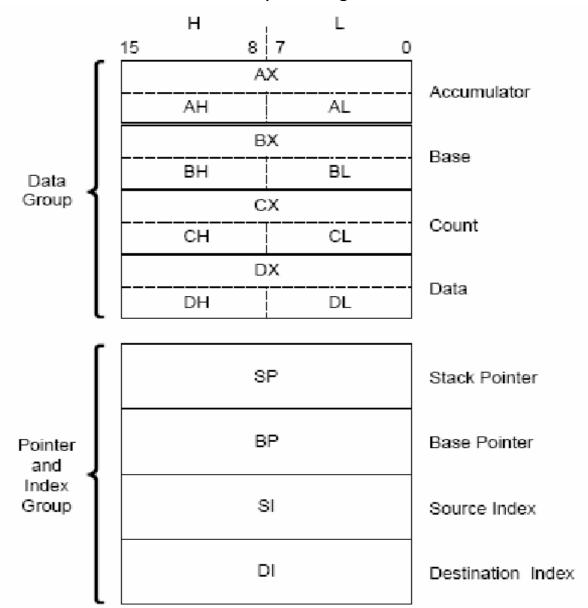

#### 1. General Purpose Registers

The data registers can be addressed by their upper or lower halves.

Each data register can be used interchangeably as a 16-bit register or two 8-bit registers.

The pointer and index registers are always accessed as 16-bit values.

The  $\mu p$  can use data registers without constraint in most arithmetic and logic operations. Arithmetic and logic operations can also use the pointer and index registers. Some instructions use certain registers implicitly allowing compact encoding.

- **SP Stack Pointer**: Always points to top item of the stack.

- **BP Base Pointer**: It is used to access any item in the stack;

- **SI Source Index:** Contains the address of the current element in the source string;

- **DI Destination Index**: Contains the address of the current element in the destination string;

Table 1. Implicit Use of General Registers

| Register | Operations                                                          |

|----------|---------------------------------------------------------------------|

| AX       | Word Multiply, Word Divide, Word I/O                                |

| AL       | Byte Multiply, Byte Divide, Byte I/O, Translate, Decimal Arithmetic |

| AH       | Byte Multiply, Byte Divide                                          |

| BX       | Translate                                                           |

| CX       | String Operations, Loops                                            |

| CL       | Variable Shift and Rotate                                           |

| DX       | Word Multiply, Word Divide, Indirect I/O                            |

| SP       | Stack Operations                                                    |

| SI       | String Operations                                                   |

| DI       | String Operations                                                   |

#### 2. Segment registers

The mp 8086 has a 20-bit address bus for 1 Mbyte external memory but inside the CPU registers have 16 bits that can access 64 Kbytes.

The 8086 family memory space is divided into logical segments of up to 64 Kbytes each. The segment registers contain the base addresses (starting locations) of these memory segments.

- **CS** (code segment) points at the segment containing the current program.

- **DS** (data segment)- generally points at the segment where variables are defined.

- **ES** (extra segment)- extra segment register, it's up to a coder to define its usage.

- SS (stack segment)- points at the segment containing the stack.

#### 3. Special purpose registers

#### **IP** - the instruction pointer or program counter:

Always points to next instruction to be executed. It contains the offset (displacement) of the next instruction from the start address of the code segment.

Flags Register - determines the current state of the processor. From 16 bits are used only 9.

| A 100 |    |    |    |    |    |    |    | Nec' |    | r |    |   |    |   |    |

|-------|----|----|----|----|----|----|----|------|----|---|----|---|----|---|----|

| 15    | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7    | 6  | 5 | 4  | 3 | 2  | 1 | 0  |

|       |    |    |    | Of | df | if | tf | sf   | Zf |   | Af |   | pf |   | cf |

#### Condition flags:

- **O bit -Carry Flag (CF)** this flag is set to **1** when there is a carry (borrow) from the 8 or 16 bit in addition or subtraction operation.

- **2 bit Parity Flag (PF)** this flag is set to **1** when there is even number of one bits in result, and to **0** when there is odd number of one bits. Even if result is a word only 8 low bits are analyzed!

- 4 bit Auxiliary Flag (AF) set to 1 when there is an unsigned overflow for low nibble (4 bits).

- 6 bit Zero Flag (ZF) set to 1 when result is zero. For none zero result this flag is set to 0.

- **7 bit Sign Flag (SF)** set to **1** when result is **negative**. When result is **positive** it is set to **0**. Actually this flag take the value of the most significant bit.

- 11 bit Overflow Flag (OF) set to 1 when there is a signed overflow.

#### Control flags:

**8 bit - Trap Flag (TF)** System flag - Used for on-chip debugging when TF=1. In this case the interrupt is generated (int 1) which calls a special routine to show the state of internal registers.

**9 bit - Interrupt enable Flag (IF)** System flag - when this flag is set to **1** CPU reacts to interrupts on INTR input of the mp from external devices. When IF=0 interrupts are not allowed (masked). IF do not react to NMI (non maskable) interrupts and to internal interrupts performed by instruction INT.

Instructions CLI (clear interrupt) and STI (set interrupt) are used to control this flag.

**10 bit - Direction Flag (DF)** - this flag is used by some instructions to process data chains, when this flag is set to **0** - the processing is done forward (increment of SI and DI registers), when this flag is set to **1** the processing is done backward - decrement

(instructions CLD and STD).

### **Exercises**

Determine the value of CF, ZF, SF, OF, PF and AF after the following addition operations:

- 1. 342Ah+57E2h=8C0Ch

- 2. E42Ah+96B8h=7AE2h

- 3. C739h+38C7h=0000h

- 4. F502h+1A7h = F6A9h

- 5. 6BD3h+90F1h=FCC4h

The FLAGS register is the status register in Intel x86 microprocessors that contains the current state of the processor. This register is 16 bits wide. Its successors, the EFLAGS and RFLAGS registers are 32 bits and 64 bits wide, respectively. The wider registers retain compatibility with their smaller predecessors.

| Intel x86                             | FLAGS Re | gister                  |                | EFL  | AGS             |          |                            |         |  |  |

|---------------------------------------|----------|-------------------------|----------------|------|-----------------|----------|----------------------------|---------|--|--|

| FLAGS                                 |          |                         |                | 16   | RF              | Resur    | me flag (386+ only)        | X       |  |  |

| 0                                     | CF       | Carry flag S            |                | 17   | VIV             | l Virtua | l 8086 mode flag (386+     | only) X |  |  |

| 1                                     | 1        | Reserved                |                | 18   | AC              | Alignr   | nent check (486SX+ onl     | ly) X   |  |  |

| 2                                     | PF       | Parity flag S           |                | 19   | VIF             | - Virtua | l interrupt flag (Pentium- | +) X    |  |  |

| 3                                     | 0        | Reserved                |                | 20   | VIP             | Virtual  | interrupt pending (Penti   | um+) X  |  |  |

| 4                                     | AF       | Auxiliary flag          | S              | 21   | ID              | Identi   | fication (Pentium+)        | Χ       |  |  |

| 5                                     | 0        | Reserved                |                |      |                 |          |                            |         |  |  |

| 6                                     | ZF       | Zero flag S             |                | 22-3 | 31              | 0        | Reserved                   |         |  |  |

| 7                                     | SF       | Sign flag S             |                |      |                 |          |                            |         |  |  |

| 8                                     | TP       | Trap flag (single step) | Χ              | RFL  | .AGS            | 3        |                            |         |  |  |

| 9                                     | IF       | Interrupt enable flag   | Χ              | 32-6 | 3               | 0        | Reserved                   |         |  |  |

| 10                                    | DF       | Direction flag          | С              |      |                 |          |                            |         |  |  |

| 11                                    | OF       | Overflow flag           | S              |      |                 |          |                            |         |  |  |

| 12, 13 IOPL I/O privilege level (286+ |          |                         |                |      | S: Status flag  |          |                            |         |  |  |

| only) X                               |          |                         |                |      | C: Control flag |          |                            |         |  |  |

| 14                                    | NT       | Nested task flag (286-  | X: System flag |      |                 |          |                            |         |  |  |

| only)                                 | X        |                         |                |      |                 |          |                            |         |  |  |

| 15                                    | 0        | Reserved                |                |      |                 |          |                            |         |  |  |

|                                       |          |                         |                |      |                 |          |                            |         |  |  |

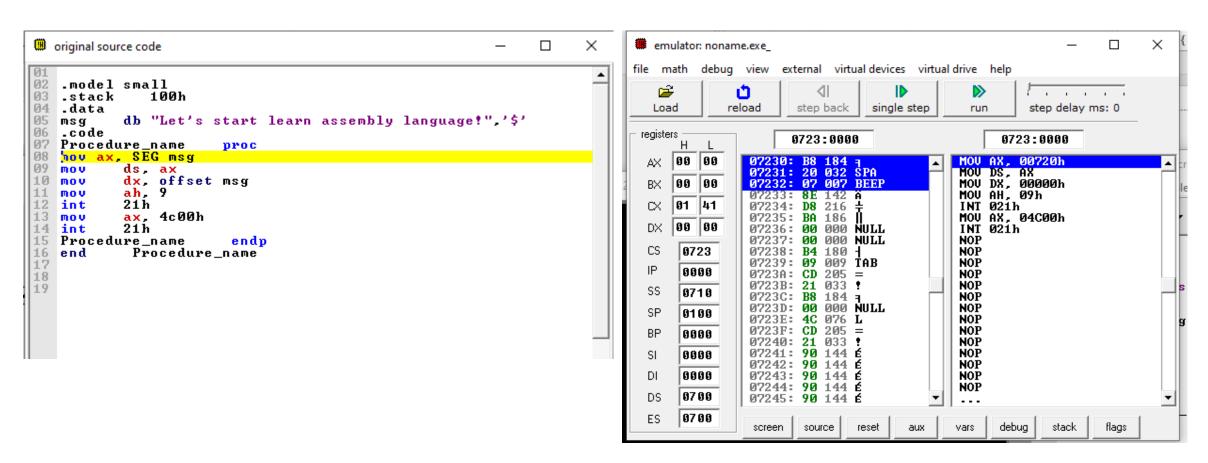

## Code exapmles

```

.model small

100h

.stack

.data

db "Let's start learn assembly language!",'$'

msg

.code

Procedure_name

proc

mov ax, SEG msg

ds, ax

mov

dx, offset msg

mov

ah, 9

mov

21h

int

ax, 4c00h

mov

21h

int

Procedure_name

endp

Procedure_name

end

```