# Московский государственный технический университет им. Н.Э. Баумана

# Ю.Б. ЦВЕТКОВ

# ПРОЦЕССЫ И ОБОРУДОВАНИЕ МИКРОТЕХНОЛОГИИ Часть 1

#### Учебное пособие

для студентов, обучающихся по направлениям «Электроника и наноэлектроника», «Наноинженерия»

Москва Издательство МГТУ им. Н. Э. Баумана 2017 УДК 621.3.049.77

ББК 32.85

Ц27

Рекомендовано Редакционно-издательским советом МГТУ им. Н. Э. Баумана в качестве учебного пособия.

| Рецензент |  |

|-----------|--|

|           |  |

|           |  |

#### Цветков, Ю. Б.

Процессы и оборудование микротехнологии. Часть 1 / Ю.Б. Цветков. — Москва: Издательство МГТУ им. Н.Э. Баумана,2017. — 168 с. : ил.

| <b>ISBN</b> | <br>    |     |       | <br>   |   |       |   |    |   |   |   |   |   |   |   |   |  |

|-------------|---------|-----|-------|--------|---|-------|---|----|---|---|---|---|---|---|---|---|--|

| IDDI 1      | <br>• • | • • | <br>• | <br>٠. | • | <br>• | • | ٠. | • | • | • | • | • | • | • | • |  |

II27 Пособие предназначено для самостоятельной проработки студентами дисциплины «Процессы и оборудование микротехнологии». Приведено описание общей последовательности процесов микротехнологии на примерах производства интегральных микросхем и кремниевого микродатчика давления. Рассмотрены основные этапы получения кремниевых монокристаллических пластин, ключевые операции микротехнологии изготовление кремниевых пластин, оксидирование, микролитография, элионные процессы, микросборка. Акцентировано внимание на взаимосвязи между свойствами материалов, структуры, устройством и электрическими характеристики микроструктур. Рассмотрены физико-химические модели и методы анализа качества технологических процессов микротехнологии. В каждом разделе пособия приведены вопросы и задания для самоконтроля.

Для студентов, обучающихся по направлениям «Электроника и наноэлектроника», «Наноинженерия».

УДК 621.3.049.77

ББК 32.85

- © Цветков, Ю. Б., 2017

- © МГТУ им. Н.Э. Баумана, 2017

- © Оформление. Издательство МГТУ им. Н.Э. Баумана, 2017

| ISBN | <br> |  |  |  |  |  |  |  |  |  |  |  |  |  |

|------|------|--|--|--|--|--|--|--|--|--|--|--|--|--|

|      |      |  |  |  |  |  |  |  |  |  |  |  |  |  |

В соответствии со ст. 1299 и 1301 ГК РФ при устранении ограничений, установленных техническими средствами защиты авторских прав, правообладатель вправе требовать от нарушителя возмещения убытков или выплаты компенсации

# ОГЛАВЛЕНИЕ

| ПРЕДИСЛОВИЕ                                                           | 4  |

|-----------------------------------------------------------------------|----|

| ВВЕДЕНИЕ                                                              | 8  |

| МОДУЛЬ 1                                                              | 18 |

| ТЕХНОЛОГИЧЕСКИЙ АНАЛИЗ ИЗДЕЛИЙ МИКРОТЕХНОЛОГИИ                        | 18 |

| Аннотация                                                             | 18 |

| Планируемые результаты обучения                                       | 18 |

| 1.1. Интегральные микросхемы как объект производства                  | 20 |

| 1.1.1. Структура и принцип действия КМОП микросхем                    | 20 |

| 1.1.2. Технология КМОП микросхем                                      | 25 |

| 1.1.2.1. Формирование карманов <i>p</i> - и <i>n</i> - типа           | 26 |

| 1.1.2.2. Формирование изоляции                                        | 28 |

| 1.1.2.3. Формирование затвора и слабое легирование истока и стока     | 30 |

| 1.1.2.4. Формирование спейсера и глубокое легирование                 | 32 |

| 1.1.2.5. Формирование контактов                                       | 35 |

| 1.1.2.6. Формирование металлических проводников: 1-й слой металла     | 37 |

| 1.1.2.7. Формирование металлических проводников: 2-й слой металла     | 39 |

| 1.1.2.8. Масштабирование КМОП микросхем                               | 42 |

| 1.1.3. Приложения                                                     | 47 |

| П.1.1. Параметры металлических межсоединений                          | 47 |

| П.1.2. Особенности формирования медных межсоединений.                 | 49 |

| П.1.3. Диэлектрические свойства материалов микротехнологии            | 53 |

| 1.1.4. Перечень ресурсов сети интернет для самостоятельной проработки | 56 |

| 1.1.5. Задания для самостоятельной работы и самоконтроля              | 57 |

### ПРЕДИСЛОВИЕ

Учебное пособие подготовлено в виде курса лекций для самостоятельной проработки студентами дисциплины «Процессы и оборудование микротехнологии», входящей в образовательную программу бакалавриата по направлению подготовки 11.03.04 «Электроника и наноэлектроника» (уровень бакалавриата), профиль «Электронное машиностроение».

**Цель изучения дисциплины** - освоение системы общих принципов, положений и методов построения наукоемких технологических процессов на примере микротехнологии/

#### После изучения дисциплины студенты овладеют:

- базовыми знаниями о номенклатуре, возможностях и перспективах развития процессов и оборудования микротехнологий,

- методами анализа и управления качеством технологических процессов,

- практическими навыками исследования и реализации ключевых процессов микротехнологии.

### Планируемые результаты обучения

Дисциплина, и, соответственно, пособие построено по модульному принципу, каждый модуль представляет собой логически завершенный раздел курса.

Для каждого модуля приводится набор планируемых результатов обучения, заданных программой дисциплины. Достижение этих результатов оценивается при текущем контроле усвоения дисциплины.

Для изучения дисциплины необходимо предварительное освоение следующих дисциплин:

- 1. Иностранный язык («Профессиональная и научная терминология»).

- 2. Математический анализ («Дифференциальное исчисление»).

- 3. Аналитическая геометрия «Векторная алгебра», «Матрицы и системы линейных алгебраических уравнений»).

- 4. Интегралы и дифференциальные уравнения.

- 5. Линейная алгебра и функции многих переменных.

- 6. Информатика.

- 7. Физика («Физические основы термодинамики», «Электричество и магнетизм», «Электромагнитные волны и оптика», «Основы квантовой теории», «Физика твердого тела».

- 8. Химия (модули «Строение вещества», «Общие закономерности протекания химических процессов», «Химические и электрохимические процессы в растворах», «Химия элементов»).

- 9. Электронная компонентная база» (модуль Физические процессы в полупроводниковых структурах», модуль «Полупроводниковые приборы).

- 10. Физико-химические основы электронных технологий.

#### Методика проработки и освоения материала модулей дисциплины

Дисциплина предназначена для достижения ряда результатов обучения, которые описывают то, что студент должен будет после освоения дисциплины **знать** (помнить и понимать), **уметь** (применять, анализировать, оценивать и даже создавать), какими важными навыками он должен **овладеть**.

Планируемые результаты обучения сформулированы в программе дисциплины, их необходимо постоянно иметь в виду при ее изучении, особенно с учетом того, что достижение каждого результата будет оценено при текущем или промежуточном контроле.

Дисциплина построена по модульному принципу, каждый модуль представляет собой логически завершенный раздел курса.

На первом занятии каждый студент получает в электронном виде полный комплекс учебно-методических материалов по дисциплине, включающий программу, лекционный курс, методические указания по лабораторным работам.

**Лекционные занятия** посвящены рассмотрению ключевых, базовых положений курса и разъяснению учебных заданий, выносимых на самостоятельную

проработку.

Семинарские занятия проводятся для закрепления усвоенной информации, приобретения навыков ее применения для решения практических задач в предметной области дисциплины.

**Лабораторные работы** предназначены для приобретения опыта практической реализации основной профессиональной образовательной программы. Методические указания к лабораторным работам прорабатываются студентами во время самостоятельной подготовки. Необходимый уровень подготовки контролируется перед проведением лабораторных работ.

В ряде разделов пособия приведены приложения, разъясняющие основные положения смежных дисциплин, используемых в данном курсе.

Для облегчения работы с пособием в него введены глоссарии, а также используется система гиперссылок на внутренние и на внешние (при наличии связи с Интернет) источники информации.

Самостоятельная работа студентов включает проработку лекционного курса, выполнение домашних заданий, подготовку рефератов и пр. Результаты всех видов работы студентов формируются в виде их личных портфолио, которые учитываются на промежуточной аттестации.

Предусматривается также расширение материала пособия в результате поиска, анализа, структурирования и представления в компактном виде современной информации их всех возможных источников.

Для этого в начале каждого раздела учебного пособия вслед за аннотацией приводятся ключевые слова на русском и английском языках. В конце каждого модуля приводятся списки дополнительной литературы и адреса источников в Интернет, которые можно использовать как начальные источники поиска информации. По ключевым словам необходимо найти дополнительную информацию по заданной теме и представить ее в виде аналитического обзора по заданным правилам. Новые термины оформить в виде глоссария, а изученный материал — в виде концептуальной карты (карты памяти).

Каждый раздел завершается списком контрольных заданий, которые необходимо проработать самостоятельно, учитывая, что аналогичные задания будут предложены при текущем контроле усвоения каждого модуля дисциплины. Их следует выполнять строго по графику учебной работы, обсуждая результаты на семинарах и консультациях.

**Текущий контроль** проводится в течение каждого модуля, его итоговые результаты складываются из следующих оценок:

- защита домашних заданий, рефератов;

- защита лабораторных работ;

- контрольные работы,

- работа на лекциях и семинарах.

Для завершения работы в семестре студент должен выполнить все контрольные мероприятия, иметь полный комплект подготовленных домашних заданий, рефератов и концептуальных карт.

Промежуточная аттестация по дисциплине (экзамен) основывается на результатах текущего контроля, а также включает дополнительное контрольное мероприятие. Оно служит для оценки владения студентом ключевыми, базовыми положениями предметной области, умением их применять, проводить оценку, анализировать и создавать объекты по задаваемым параметрам.

Освоение дисциплины, ее успешное завершение на стадии промежуточного контроля (экзамена) возможно только при регулярной работе во время семестра и планомерном прохождении текущего контроля. Создать портфолио по трем модулям в каждом семестре, пройти по каждому модулю плановые контрольные мероприятия в течение экзаменационной сессии **невозможно.**

### **ВВЕДЕНИЕ**

Одно из основных направлений развития современной техники – микроминиатюризация и повышение функциональности ее изделий.

Термин микроминиатюризация был введен в 50-х годах прошлого века американскими разработчиками электронной аппаратуры для первых спутников. Примечательно, что изначально приставка микро в этом термине воспринималось как гипербола. Микроминиатюризация с применением электронных ламп и первых транзисторов обеспечивала всего лишь создание электронной аппаратуры с размерами меньшими, чем те, которые до этого считались миниатюрными.

Однако через два-три десятилетия этот термин приобрел буквальное значение — электронные устройства становились все миниатюрнее, при этом размеры электронных компонентов уменьшились, а их функциональные возможности увеличились радикально.

Поэтому термин микроэлектроника уже не был гиперболой. Он точно описывал новый раздел электроники, связанный с изучением и производством изделий, отдельные элементов которых были уменьшены до микронных и субмикронных и нанометровых размеров.

Бурное развитие микроэлектроники в последние десятилетия стало возможным благодаря разработке и непрерывному совершенствованию технологических методов, обеспечивающих массовое производство микроструктур с уникальными техническими параметрами и приемлемыми экономическими показателями.

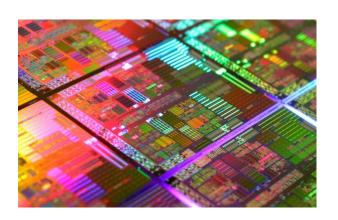

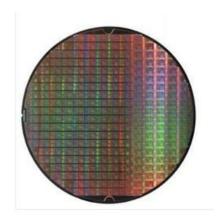

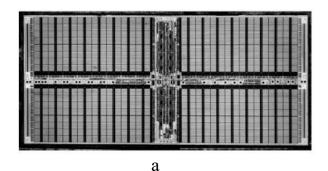

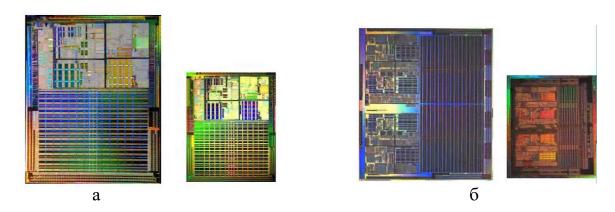

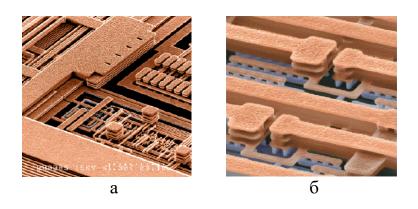

В наиболее полной мере эти методы реализованы в полупроводниковом производстве при изготовлении интегральных микросхем – ИМС (рис. В1), а в последнее время - микроэлектромеханических систем – МЭМС (рис. В2).

Именно в этих областях достигнуты наиболее впечатляющие практические результаты — резко увеличены быстродействие микропроцессоров и объемы запоминающих устройств, радикально уменьшены размеры и повышена чувствительность кремниевых микродачиков.

Рис. В1. Интегральные микросхемы а - топологии отдельных кристаллов, б – кремниевая подложка (групповая заготовка)

Повышение функциональных возможностей микроэлектронных компонентов привело к увеличению числа их выводов и, соответственно, к возрастанию плотности монтажа на подложках гибридных ИМС и микросборок, на многослойных печатных платах. Размеры проводников на этих изделиях уже сейчас составляют 20...50 мкм, непрерывно возрастают также их функциональные возможно-

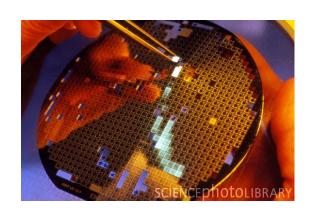

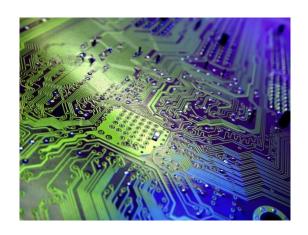

сти. Тенденция к микроминиатюризации микроэлектронных компонентов очевидна. Не менее очевиден и уже проявляется перенос методов технологии микроэлектроники в производство электронной аппаратуры, например, при изготовлении печатных плат также используются групповые заготовки (рис. В3).

Рис. В3. Печатные платы а - топология, б – групповая заготовка

Технологические возможности микроэлектроники послужили основой для появления и бурного развития не только микросистемной техники, но и оптоэлектроники, они все боле широко используются при изготовлении дифракционных оптических элементов и микроформованных деталей по технологии LIGA (Litographie, Galvanoformung и Abformung – нем. - литография, гальваностегия, формовка).

Приведенный, далеко не полный, список объектов микроминиатюризации включает весьма разнородные по функциональному назначению и по параметрам изделия. Вместе с тем, с технологической точки зрения все они имеют ряд общих признаков.

Все они являются плоскими, многослойными структурами, их функциональные элементы выполнены в виде микрорельефов в технологических слоях. Связь между слоями осуществляется электропроводящими микропереходами, при этом соответствующие элементы слоев должны быть точно совмещены между со-

бой. Внешние слои микроструктур должны быть подготовлены для контактирования с другими изделиями при сборке.

Уникальные возможности применяемых для изготовления таких структур технологических методов, оригинальность технических решений, их универсальность - все это характерные черты самостоятельного научно-технического направления, окончательно сформировавшегося в технике к концу 20-го столетия и получившего название микротехнология (microtechnology, microrfabrication, microfabrication technology).

**Микротехнология** представляет собой совокупность методов и технических средств (оборудования, инструментов, используемых материалов), применяемых для исследования, разработки и производства сверхминиатюрных приборов и устройств, элементы которых имеют микро- и нанометровые размеры.

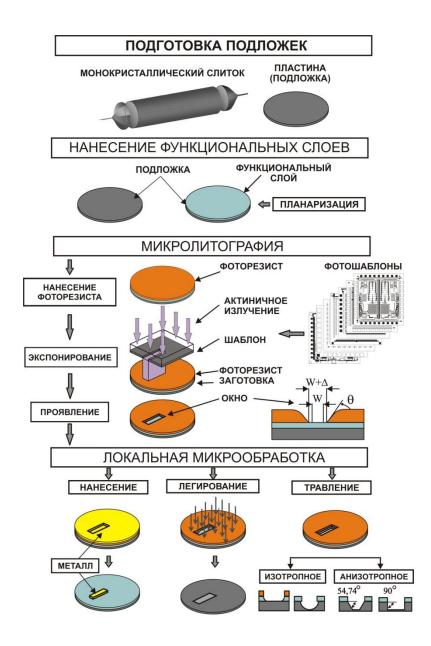

Поскольку основу микротехнологии составляет комплекс групповых прецизионных технологий, разработанных для производства микроэлектроники, в них укрупненно можно выделить следующие этапы (рис. В4):

- изготовление монокристаллических кремниевых подложек;

- формирование на поверхности заготовок тонких функциональных слоев;

- создание на поверхности слоя защитной маски с локальными окнами;

- микрообработка функционального слоя через окна в маске;

- микросборка.

**Подложки** (wafers) - это заготовки для формирования микроструктур. Обычно это тонкие пластины из монокристаллического кремния, к структуре, физическим и геометрическим параметрам которых предъявляются особые, часто беспрецедентные в технике требования.

**Нанесение функциональных слоев** реализуется методами элионных технологий, позволяющих с помощью электронных, ионных, атомарных и молекулярных потоков и сред создавать на поверхности подложек полупроводниковые, проводящие и диэлектрические слои толщиной от нескольких нанометров до единиц микрометров. Наиболее распространены методы нанесения тонких слоев ва-

куумным напылением (physical vapour deposition - PVD) и химическим осаждением из паровой фазы (chemical vapour deposition -CVD).

Рис. В4. Основные этапы и процессы микротехнологии

Далее используется **микролитография** (*microlithography*), которая позволяет локализовать зоны воздействия на заготовку. Для этого на ее поверхность наносится тонкая чувствительная к актиничному излучению полимерная пленка (резист), которая затем экспонируется через шаблон с требуемым рисунком (то-

пологией).

При последующем проявлении происходит локальное удаление участков резиста, образуются окна требуемых размеров и формы, через которые возможен доступ к поверхности заготовки (рис.4). Окна в резисте, их размеры и профиль, должны отвечать чрезвычайно жестким требованиям, поскольку они определяют качество третьего этапа микротехнологии.

**Микрообработка** (*micromachining*) обеспечивает локальное воздействие на заготовку: нанесение материала, легирование поверхности заготовки или ее травление. При микрообработке воздействие обрабатывающей среды ограничивается (локализуется) окнами в резисте. Арсенал современных методов микрообработки весьма широк. Для локального нанесения могут использоваться уже упомянутые методы элионных технологий, например вакуумное напыление, химическое осаждение из паровой фазы, а также гальваническое наращивание.

Локальное легирование проводится методами диффузии из парогазовой смеси или ионным легированием.

Локальное травление (изотропное или анизотропное) выполняется жидкостными травителями или с использованием плазменных методов, создающих требуемый профиль микроструктур.

Важной особенностью микротехнологии является групповой метод обработки — за один цикл экспонирования формируются миллионы окон в пределах одного модуля на заготовке, а затем также одновременно через эти окна заготовка подвергается микрообработке.

Возможность одновременного и относительно быстрого получения огромного числа элементов структур с микронными и субмикронными размерами оказала революционное воздействие на развитие микротехнологии.

**Микросборка** (packaging, assembly) начинается с разделения подложки на отдельные кристаллы и включает монтаж кристаллов на коммутационную плату или в корпус (die placing), электрическое соединение элементов кристалла с внешними выводами (wire bonding), а также его герметизацию (packging).

Даже краткое рассмотрение основных этапов микротехнологии показывает, что для ее реализации используется очень широкий спектр технологических процессов. В их число входят как универсальные, широко применяемые технологии, так и уникальные процессы, разработанные специально для создания микроструктур.

При этом даже универсальные технологии, которые используются в основном на этапе создания подложек (заготовок), сопровождаются весьма специфическими процессами.

Например, после металлургических процессов литейного производства применяются методы тонкой химической очистки поликристаллических слитков, выращивание монокристаллов и их глубокая очистка. Последующая механическая обработка (резка, шлифовка, полировка) полупроводниковых слитков и пластин выполняется только алмазными абразивными инструментами и методами химико-механической обработки.

На этапах нанесения функциональных слоев и их микрообработки применяется технологии, которые основываются на совершенно иных принципах, нежели технологии, имеющие дело с макротелами.

Так, элионные процессы — это процессы воздействия потоков высокоэнергетических частиц в вакууме на обрабатываемые материалы и изделия. Характер воздействия зависит от типа частиц (электроны, ионы, атомы, молекулы, газоразрядная плазма), от их энергии и химической активности, а также от материала твердого тела (металлы, полупроводники, диэлектрики и т. п.). В качестве среды обработки помимо вакуума используют парогазовые смеси, растворы реактивов, а сама обработка часто ведется при высокой температуре, которая должна поддерживаться с очень высокой точностью.

Не менее специфичны **процессы микролитографии**, обеспечивающей локализацию зоны обработки и позволяющей одновременно формировать на поверхности заготовки множество (до сотен миллионов) окон с микронными и субмикронными размерами элементов.

Большинство процессов микротехнологий строятся на основе применения в производстве современных достижений фундаментальных наук, т.е. относятся к наукоемким технологическим процессам.

Для достижения, поддержания и управления чрезвычайно жесткими, зачастую беспрецедентными параметрами процессов микротехнологии требуется применение как физических, так и статистических методов.

Современная микротехнология доведена до промышленного уровня, усилиями ученых разных стран разработаны научно-технологические основы производства микроструктур на основе групповой прецизионной обработки.

# СТРУКТУРА ДИСЦИПЛИНЫ

Дисциплина «Процессы и оборудование микротехнологии» включает шесть модулей, изучаемых последовательно в течение двух семестров.

Модуль 1 «Технологический анализ изделий микротехнологии» посвящен рассмотрению и анализу устройства и технологии изготовления двух основных представителей микроминиатюрных изделий - интегральной микросхемы и кремниевого микродатчика.

Модуль 2 «Изготовление монокристаллических кремниевых подложек» содержит краткую информацию о свойствах монокристаллического кремния, анализ методов получения монокристаллических слитков с заданными физическими параметрами. В модуле рассмотрены способы изготовления массовых заготовок микротехнологии — кремниевых подложек - для различных сфер их применения, от солнечных батарей до микроэлектроники.

Модуль 3 «Элионные процессы » включает информацию о методах и оборудовании для нанесения тонких пленок в вакууме, химического осаждения из паровой фазы, осаждения диэлектрических пленок и поликристаллического кремния, газофазной и молекулярно-лучевой эпитаксии.

В модуле 4 «Микролитография» рассматриваются области применения, основные этапы и структурные элементы процесса, его место в микротехнологии. Проводится сравнение позитивных и негативных фоторезистов, анализируются фотохимические процессы при экспонировании, методы и оборудование для формирование тонких пленок фоторезистов. В модуле рассмотрены также источники актиничного излучения, системы экспонирования, методы и оборудование для изготовления фотошаблонов и проведения операций совмещения и экспонирования.

Модуль 5 «Микрообработка» содержит три основных раздела, соответствующих видам локального воздействия на заготовку: нанесение материала (осаждение из жидкостной или парогазовой фазы), легирование поверхности заготовки (ионное легирование, диффузия) или ее травление (жидкостное и плазменное).

Отдельно рассматриваются LIGA технология, трехмерная объёмная микрообработка монокристаллического кремния и его поверхностная микрообработка с наращиванием слоев микроструктур.

Модуль 6 «Микросборка» охватывает основные операции по подготовке и проведению сборки микроструктур. В их число входят такие подготовительные операции, как утонение (шлифовка) подложек, их разделение на кристаллы, последующий монтаж кристаллов в корпус и присоединение электродных выводов с последующей герметизацией.

Для каждого этапа предусмотрен анализ применяемых методов и соответствующего оборудования. Дополнительно рассматриваются методы сборки, применяемые в технологии МЭМС — соединение кремниевых пластин со стеклом и между собой.

## МОДУЛЬ 1.

# ТЕХНОЛОГИЧЕСКИЙ АНАЛИЗ ИЗДЕЛИЙ МИКРОТЕХНОЛОГИИ

#### Аннотация

Анализ изделий микроэлектроники с позиции технолога позволяет оценить комплекс требований к основным элементам технологической системы – к материалам (заготовок и элементов микроструктур), методам их формирования, применяемому оборудованию.

Поэтому первый модуль дисциплины «Процессы и оборудование микротехнологий» посвящен технологическому анализу типовых изделий микротехнологии — интегральной микросхемы и кремниевого микродатчика давления.

Кратко рассмотрены принцип действия, структура и параметры современной интегральной микросхемы на основе МОП структуры. Выделены основные этапы процесса изготовления КМОП инвертора: формирование: карманов р- и п- типа, щелевой изоляции, областей истока, стока и затвора, контактов к активным областям, многослойной металлизации. Описано назначение операций процесса, приведены режимы и применяемые материалы. Дополнительно рассмотрены особенности масштабирования КМОП микросхем, параметры металлических межсоединений, технология медных межсоединений - инкрустирование (damascene).

Описан принцип действия кремниевого микродатчика давления, его технические характеристики, маршрут и особенности основных операций изготовления чувствительного элемента из монокристаллического кремния. Приведена последовательность формирования пьезорезисторов мостовой схемы чувствительного элемента, формирования контактов к ним и получение упругой диафрагмы. Дополнительно рассмотрена суть тензо- и пьезоэффекта в кремнии.

**Ключевые слова:** КМОП инвертор, процесс изготовления, карманы, щелевая изоляции, исток, сток, затвор, контакты к активным областям, многослойная металлизация, damascene, кремниевая мембрана, пьезоэффект в кремнии, пьезорезисторы, мостовая схема.

# Планируемые результаты обучения

После изучения модуля «Технологический анализ изделий микротехнологии» Вы сможете:

• перечислить и объяснить не менее двадцати понятий и терминов, в том числе на английском языке, описывающих процесс изготовления изделий микротехнологии, дать формулировки их назначения и выполняемых функций;

- представить в виде блок-схем типовые маршруты изготовления заданных изделий, выделить в применяемых материалах проводники, диэлектрики, полупроводники;

- привести в соответствие формируемые микроструктуры и применяемые для этого фотошаблоны;

- для заданного изделия микротехнологии: продемонстрировать взаимосвязь конструктивных элементов изделий и технологических процессов их изготовления; провести его технологический анализ, выявить и обозначить лимитирующие параметры и критические операции;

- для заданного технологического процесса микротехнологии выбрать характеризующие его ключевые термины и провести по ним поиск среде Интернет, в том числе иноязычной, обобщить и провести анализ информации по современному состоянию и перспективам развития процесса;

- представлять результаты работы с информацией в виде концептуальных карт (карт памяти), аналитических обзоров и презентаций по заданным правилам.

# 1.1. Интегральные микросхемы как объект производства

В первом разделе модуля «Технологический анализ изделий микротехнологии» приведены краткие сведения о принципе действия полупроводниковых приборов на примере МОП транзисторов, структура и принцип действия интегральной микросхемы на основе КМОП инвертора.

Основное внимание уделено рассмотрению маршрута и особенностям ключевых операций планарной технологии изготовления твердотельных интегральных микросхем.

# 1.1.1. Структура и принцип действия КМОП микросхем

Полупроводниковые интегральные микросхемы (ИС) являются основным *массовым* объектом современных микротехнологий.

Непрерывное совершенствование ИС является катализатором прогресса важнейших отраслей народного хозяйства, поэтому уровень и объемы производства ИС определяют научно-технический и оборонный потенциалы развитых стран.

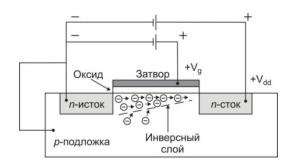

Подавляющее большинство современных микросхем (и цифровых, и аналоговых) построено на полевых или МОП (металл - окисел - полупроводник) транзисторах. Различают p-МОП (p-канальные) и n-МОП (n-канальные) транзисторы.

Структуры n и p-канальных МОП-транзисторов аналогичны и отличаются видом носителей (электроны и дырки соответственно), переносящих заряд от uc-moka к cmoky при приложении noporoboro hanpsжения.

Так, n-МОП обозначает транзистор, в котором области истока и стока имеют n-тип проводимости, сформированные в nodnoжке p-типа. Область между истоком и стоком формирует kahan, над которым размещен металлический или поликремниевый kahan, отделенный от канала kahan kahan

При подаче на затвор положительного напряжения возникает электрическое поле, отталкивающее от него носители заряда p-типа - положительные дырки (рис. 1.1). В то же время оно притягивает в область канала электроны. По дости-

жении порогового напряжения количество электронов в канале существенно превосходит количество дырок — происходит *инвертирование*. При этом образуется проводящий канал n-типа, соединяющий исток со стоком, причем подзатворный диэлектрик предотвращает попадание электронов в затвор.

Рис. 1.1. Структура n-МОП транзистора

Аналогично, p-МОП транзистор содержит исток и сток в виде областей p-типа в подложке n-типа, а основными переносчиками заряда являются дырки. Подача на затвор отрицательного напряжения ведет к инвертированию и формированию канала p-типа.

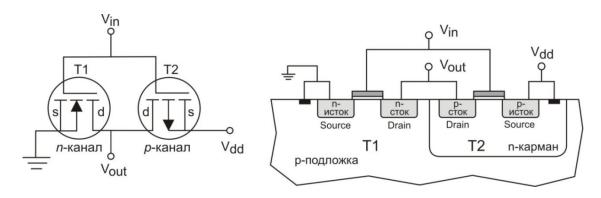

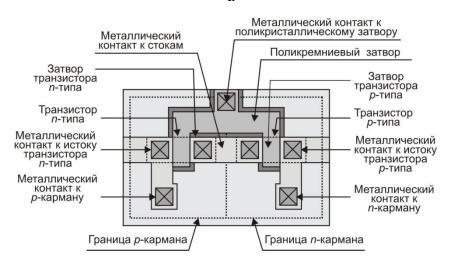

Объединение пары дополняющих друг друга (*комплементарных*) n-МОП и p-МОП транзисторов в единую КМОП структуру позволяет получить, например, схему инвертора, широко применяемого в современных микросхемах (рис. 1.2).

Рис. 1.2. КМОП инвертор

а – принципиальная схема, б – структура

В инверторе транзисторы Т1 и Т2 соединены последовательно так, что к их

затворам подведено общее входное напряжение  $V_{in}$ , а стоки имеют общий выход  $V_{out}$  (рис. 1.2, a).

В n-канальном транзисторе Т1 подложка p-типа обозначена стрелкой, направленной внутрь, а в p-канальном транзисторе Т2 подложка n-типа обозначена стрелкой, направленной наружу.

Подложка n-канального транзистора Т1 соединена с землей, а на подложку p-канального транзистора Т2 подается напряжение питания  $V_{dd}$  (около +5 B).

Инвертор работает следующим образом. При подаче высокого входного напряжения  $V_{in}$  (сопоставимого с  $V_{dd}$ ) n-канальный транзистор Т1 включается (см. выше описание работы n-МОП транзистора).

Напряжение между затвором и подложкой p-канального транзистора Т2 при этом близко к нулю, поскольку и затвор и подложка имеют один и тот же потенциал  $V_{dd}$ . Поэтому транзистор Т2 будет выключен, а выходное напряжение будет низким.

Если же входное напряжение  $V_{in}$  будет низким (близко к потенциалу земли), n-канальный транзистор Т1 выключится. Напряжение между затвором и подложкой p-канального транзистора Т2 будет теперь равно - $V_{dd}$ , поскольку потенциалы затвора и подложки равны 0 и + $V_{dd}$  соответственно.

Поскольку пороговое напряжения p-канального транзистора составляет примерно  $V_t = -2$  В, то он включится и выходное напряжение будет высоким.

Таким образом, при подаче на вход инвертора высокого напряжения (логическая 1) получаем на выходе низкое напряжение — логический 0. Напротив, низкое напряжение на входе (логический 0) дает на выходе высокое напряжение — логическую 1.

Отметим важное обстоятельство. Для формирования инвертора в виде микросхемы на едином кремниевом кристалле необходимо учесть, что подложки транзисторов T1 и T2 имеют разный тип проводимости: p и n соответственно.

При этом кремниевые подложки, полученные из монокристаллических слитков, имеют вполне определенный тип проводимости по всему рабочему полю.

Для решения этой проблемы в подложке создается локальная область с противоположным типом проводимости —  $\kappa$  (см. рис. 1.2, б), в которых формируется один из транзисторов (часто — оба).

Отметим, что в инверторе помимо контактов к стокам, истокам и затворам транзисторов формируются также контакты к подложке и к выделенному в ней карману. Так, p-подложка n-канального транзистора T1 соединена с землей.

Напротив, n-карман p-канального транзистора Т2 подключен к источнику питания  $V_{dd}$  (примерно +5 В). Таким образом, каждый транзистор имеет четыре контакта к своим активным элементам. При этом ucmok всегда подключен к подложке (или карману) и имеет с ней один потенциал.

Поскольку p-подложка подключена к земле, а n-карман — к положительному потенциалу, они образуют обратно смещенный p-n переход, предотвращая протекание между ними электрического тока.

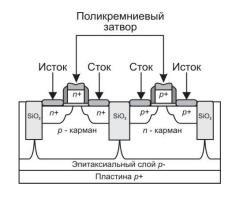

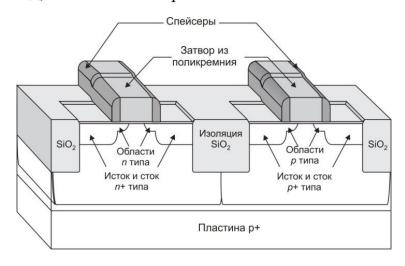

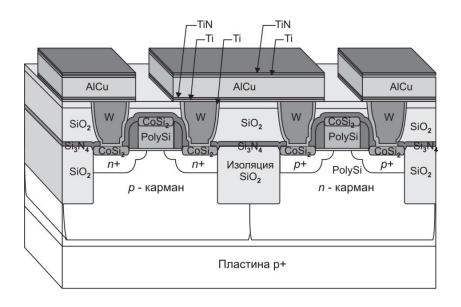

КМОП структуры современных ИС, в частности, инверторы (рис. 1.3), имеют минимальные размеры структур в диапазоне 25-180 нм. В рассматриваемом примере слой, в котором сформированы карманы МОП транзисторов — это эпимаксиальный слой p- типа толщиной 2 -5 мкм, который наращивается на сильно легированную пластину кремния p+ типа.

Сочетание сильно- и слаболегированных слоев кремния позволяет предотвратить «защелкивание» транзисторов и уменьшает вероятность их деградации.

a

б

Рис. 1.3. Структура (а) и топология (б) современного КМОП инвертора

В слаболегированном эпитаксиальном слое выполнен не только n-карман (как на рис. 1.2, б), но дополнительно и p-карман. В этих карманах формируются МОП транзисторы (рис. 1.3, а, б). В p-кармане выполнен транзистор n-МОП типа, который включает две сильно легированные близлежащие области n+ типа (исток и сток). Над узкой промежуточной областью между стоком и истоком размещен тонкий (200 нм и менее) изолирующий слой диоксида кремния  $SiO_2 - nod$  затворный диэлектрик. На него нанесен слой металла или легированного поликремния n+ типа (poly Si), который служит управляющим электродом – затвором.

По обеим сторонам поликремниевого затвора сформированы *спейсеры* – разделители, которые изолируют затвор от контактов стока и истока.

На поверхности стока, истока и затвора локально нанесен *силицид* (например, силицид кобальта CoSi<sub>2</sub>) для электрического контакта к этим элементам.

В современных МОП-транзисторах используются мелкие *слаболегирован*ные области (LDD - Lightly Doped Drain), которые продлевают области истока и стока в сторону канала. Концентрация примеси (фосфор и бор) этой области составляет (4-10) $10^{18}$  см<sup>-3</sup>, в то время как в n+ областях она достигает (5-10) $10^{19}$  см<sup>-3</sup>.

Транзистор p-МОП отличается от транзистора n-МОП типа тем, что в нем исток и сток —две сильно легированные области p+ типа, а сам он выполнен в кармане n типа. Затвор этого транзистора типа выполнен из поликремния p+ типа.

Напомним, что активные области двух транзисторов КМОП ИС разделены изоляцией из оксида кремния  $SiO_2$ .

Геометрические параметры КМОП инвертора приведены в таблице 1.1.

Параметры КМОП инвертора

Таблица 1.1

| ПАРАМЕТР                                         | ЗНАЧЕНИЯ |

|--------------------------------------------------|----------|

| Толщина подзатворного диэлектрика, нм            | 3        |

| Минимальная ширина затвора, нм                   | 140      |

| Толщина поликремния, нм                          | 250      |

| Допустимые рассовмещения, нм                     | 25       |

| Шаг проводников на 1 уровне металлизации, нм     | 500      |

| Толщина проводников на 1 уровне металлизации, нм | 480      |

| Шаг проводников на 2 уровне металлизации, нм     | 640      |

| Толщина проводников на 2 уровне металлизации, нм | 700      |

| Габариты контактных площадок, мкм                | 100x100  |

# 1.1.2. Технология КМОП микросхем

В технологическом процессе КМОП микросхемы можно выделить несколько важных этапов, на которых формируются:

- карманы *p* и *n*-типа,

- изоляция между областями *p* и *n* канальных транзисторов,

- области истока, стока и затвора,

- контакты к активным областям,

- многослойная металлизация.

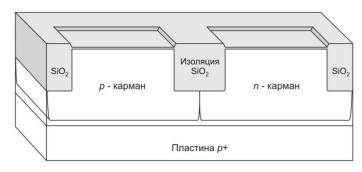

#### 1.1.2.1. Формирование карманов *p*- и *n*- типа

Создание КМОП структуры обычно начинается с выделения активных зон — карманов p-и n-типа (см. рис. 1.3), в которых будут размещаться, соответственно, n-МОП и p-МОП транзисторы. Предварительно на поверхность пластины из монокристаллического кремния ориентации (100) p+ типа проводимости наносится эпитаксиальный слой p- типа с удельным сопротивлением 5-50 Ом·см. Именно в этом слое и формируется активная структура ИС.

Кремниевые пластины подвергаются жидкостной очистке и сушатся. С их поверхностей удаляются тонкие пленки естественного оксида ( $native\ oxide$ ) SiO<sub>2</sub> толщиной в несколько десятков ангстрем, образующегося на поверхности кремния даже при комнатной температуре под воздействием влаги воздуха.

После этого на кремниевых пластинах наращивается слой защитного жертвенного слоя  $SiO_2$  толщиной 10-15 нм. Он служит для защиты поверхности эпитаксиального слоя от загрязнений и обеспечивает повышение качества последующего ионного легирования.

Создание областей разного типа проводимости (карманов p- и n- типа) выполняется с помощью фотолитографии (рис. 1.4).

В фоторезисте формируется защитная маска, через которую последовательно проводится локальное травление оксида а затем - ионное легирование сначала бором (p -тип проводимости), а затем фосфором (n -тип).

После каждого легирования фоторезист удаляется, пластина подвергается жидкостной химической очистке и быстрому термическому отжигу для активации легирующих примесей. В завершение с поверхности пластины удаляется использованный защитный слой и наносится новый, толщиной также 10-15 нм.

| Эскиз                  | Операции                                                                                                                                                      |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ФР<br>р -<br>карман    | <ul> <li>Нанесение фоторезиста и вскрытие окон по форме <i>p</i>- карманов</li> <li>Ионная имплантация бора для формирования <i>p</i>-карманов</li> </ul>     |

| ФР<br>SiO <sub>2</sub> | <ul> <li>Нанесение фоторезиста и вскрытие окон по форме <i>n</i>- карманов</li> <li>Ионная имплантация фосфора для формирования <i>n</i>- карманов</li> </ul> |

| р - п - карман         | <ul> <li>Удаление фоторезиста предыдущей операции</li> <li>Быстрый термический отжиг легированных областей карманов</li> </ul>                                |

Рис. 1.4. Этапы формирования карманов p-и n- типа

Структура ИС со сформированными карманами показана на рис. 1.5.

Рис. 1.5. Карманы *p*- и *n*- типа

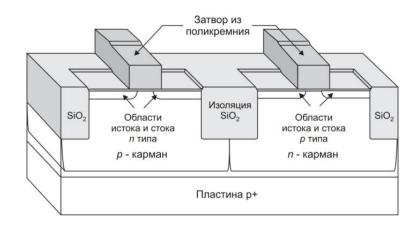

# 1.1.2.2. Формирование изоляции

Для изоляции ИС с топологической нормой менее 180 нм обычно используются мелкие канавки — щели (*shallow trenches*) шириной 140 нм и глубиной 400 нм, заполненные окисью кремния  $SiO_2$ . (рис. 1.6).

| Эскиз                                                                               | Операции                                                                                                                                                                         |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Фоторезист Si <sub>3</sub> N <sub>4</sub> SiO <sub>2</sub> SiO <sub>2</sub>         | <ul> <li>Осаждение слоя Si<sub>3</sub>N<sub>4</sub></li> <li>Нанесение слоя фоторезиста и проведение фотолитографии</li> </ul>                                                   |

| Бі <sub>3</sub> N <sub>4</sub> р - карман SiO <sub>2</sub>                          | <ul> <li>Травление слоя Si<sub>3</sub>N<sub>4</sub></li> <li>Травление слоя SiO<sub>2</sub></li> <li>Травление мелких канавок в кремнии</li> <li>Удаление фоторезиста</li> </ul> |

| р - карман Si <sub>3</sub> N <sub>4</sub> Si <sub>0</sub> 2                         | ■ Наращивание тонкого слоя SiO <sub>2</sub> для закругления углов канавок                                                                                                        |

| Si <sub>3</sub> N <sub>4</sub> SiO <sub>2</sub> ——————————————————————————————————— | <ul> <li>■ Наращивание толстого слоя SiO<sub>2</sub> для заполнения канавок</li> </ul>                                                                                           |

| Si <sub>3</sub> N <sub>4</sub> SiO <sub>2</sub>                                     | ■ Химико-механическое полирование $SiO_2$ до слоя $Si_3N_4$ - планаризация                                                                                                       |

| SiO <sub>2</sub> р - п - карман                                                     | ■ Удаление слоя Si <sub>3</sub> N <sub>4</sub>                                                                                                                                   |

Рис. 1.6. Операции формирования изоляции

Полученная ранее пленка  $SiO_2$ , помимо защиты поверхности эпитаксиального слоя от загрязнений, выполняет роль прокладочного оксида (*pad oxide*). Она сглаживает механические напряжения между кремнием и последующим функциональным слоем нитрида кремния  $Si_3N_4$  толщиной 100-250 нм, наносимым химическим осаждением из паровой фазы.

Проводится фотолитография: наносится и сушится слой фоторезиста толщиной 0,5-1 мкм, он экспонируется через фотошаблон и проявляется. В результате на поверхности пластины формируется защитная фоторезистивная маска с заданной топологией щелевой изоляции. Через эту маску последовательно травятся пленки  $Si_3N_4$  (реактивным ионным травлением), а затем  $SiO_2$  и непосредственно кремний - во фторсодержащей плазме.

В результате в кремнии формируются канавки под щелевую изоляцию заданной формы. После этого фоторезист удаляют.

Пластина снова подвергается термическому оксидированию ( $1000^{\circ}$ C), тонкий слой SiO<sub>2</sub> покрывает стенки образовавшихся канавок, скругляя их углы.

Далее плазмохимическим нанесением  $SiO_2$  этом канавки заполняются толстым слоем оксида. Последующая химико-механическая полировка поверхности пластины обеспечивает ее планаризацию. При этом слой оксида удаляется вплоть до поверхности  $Si_3N_4$ , который выполняет в данном случае роль стоп-слоя, поскольку скорость его полировки значительно ниже, чем у  $SiO_2$ . После планаризации слой  $Si_3N_4$  удаляется жидкостным химическим травлением в горячей фосфорной кислоте  $H_3PO_4$  или в плазме  $CH_2F_2$ .

Полученная структура с изоляцией показана на рис. 1.7.

Рис. 1.7. Щелевая изоляция мелкими канавками

# 1.1.2.3. Формирование затвора и слабое легирование истока и стока

Карманы p- и n- типа — это области размещения ключевых элементов МОП транзистора — истока, стока, затвора. Формирование этих элементов (рис.1.8) начинается с удаления тонкого слоя  $SiO_2$ , остающегося над карманами с предыдущих операций.

| Эскиз                         | Операции                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Подзатворный SiO <sub>2</sub> | <ul> <li>Удаление тонкого слоя SiO<sub>2</sub></li> <li>Наращивание тонкого жертвенного слоя SiO<sub>2</sub> и его удаление</li> <li>Наращивание подзатворного SiO<sub>2</sub></li> <li>Отжиг подзатворного SiO<sub>2</sub> в NO для формирования слоя азота на границе Si - SiO<sub>2</sub></li> <li>Осаждение поликремния</li> <li>Осаждение Si<sub>3</sub>N<sub>4</sub></li> </ul> |

|                               | <ul> <li>Нанесение фоторезиста и вскрытие окон по форме областей стока-истока</li> <li>Травление слоя Si<sub>3</sub>N<sub>4</sub></li> <li>Травление поликремния с остановкой на SiO<sub>2</sub></li> </ul>                                                                                                                                                                           |

|                               | <ul> <li>Удаление фоторезиста</li> <li>Удаление Si<sub>3</sub>N<sub>4</sub></li> <li>Оксидирование поликремния</li> <li>Нанесение фоторезиста и вскрытие окон по форме областей <i>p</i>-типа</li> <li>Ионное легирование областей <i>p</i> -типа бором</li> </ul>                                                                                                                    |

|                               | <ul> <li>Удаление фоторезиста</li> <li>Нанесение фоторезиста и вскрытие окон по форме областей <i>n</i>-типа</li> <li>Ионное легирование областей <i>n</i>-типа мышьяком</li> </ul>                                                                                                                                                                                                   |

Рис. 1.8. Операции формирования областей истока, стока, затвора

Пластины подвергаются очистке, причем для получения ювенильно чистых поверхностей кремния в этих зонах проводится наращивание тонкого жертвенного слоя подзатворного  $SiO_2$ .

Далее этот слой удаляется травлением в плавиковой кислоте вместе с возможными включениями и дислокациями.

После очередной очистки на пластины наращивается слой подзатворного окисла  $SiO_2$  толщиной 2-10 нм с неравномерностью по пластине не более  $\pm 0,1$  нм. После этого следует быстрый термический отжиг в атмосфере оксида азота NO для формирования насыщенного азотом слоя на границе раздела  $Si - SiO_2$ . Этот слой способствует подавлению горячих носителей заряда и противодействует диффузии легирующих веществ из поликремниевого затвора в расположенную под ним область канала.

Далее на пластину осаждается слой поликристаллического кремния (поликремний, поли-Si) толщиной 150-300 нм. Поликристаллический кремний состоит из множества небольших случайно ориентированных кристаллов. Легированный поликремний проводит электрический ток и часто используется как альтернатива металлу при соединении элементов в интегральных схемах. Поликремний покрывается тонким слоем нитрида кремния  $Si_3N_4$ , выполняющим роль антиотражающего покрытия при последующем формировании затвора.

После фотолитографии на поверхности пластины остается слой фоторезиста с окнами по форме областей стока-истока. Через эти окна травятся слои  $Si_3N_4$  и поликремния с остановкой на  $SiO_2$ . После этого фоторезист и  $Si_3N_4$  удаляются, поликремний оксидируется и на пластину наносится новый слой фоторезиста.

Последующая фотолитография оставляет закрытыми участки пластины с карманами n- типа, полностью открывая участки карманов p- типа.

Далее следует ионное легирование мышьяком на небольшую глубину для формирования слабо легированных n-областей истока-стока. При этом зона легирования ограничена поликристаллическим затвором и изоляцией  $SiO_2$  в мелких канавках. Как поликремний, так и  $SiO_2$  блокируют ионы легирующего вещества,

локализуя области его прохождения в кремний. Так реализуется принцип самосовмещения областей стока-истока с затвором.

После формирования в кармане *p*- типа областей стока-истока *n*-типа фоторезист удаляется и проводится следующая фотолитография для вскрытия окон на участках карманов *n*-типа. Ионное легирование бором формирует области истокастока *p*- типа. В этом случае, как и в предыдущем, также реализован принцип самосовмещения краев областей истока и стока с краями поликремниевого затвора. Самосовмещение обеспечивает минимальные емкости затвор—сток, затвор-исток и высокое быстродействие транзистора.

В результате ионным легированием без дополнительной маски формируют мелкозалегающие и слаболегированные области стоков и истоков, контактирующие с каналом (*LDD - Lightly Doped Drain*) (рис.1.9).

Рис. 1.9. Области истока, стока, затвора

# 1.1.2.4. Формирование спейсера и глубокое легирование

При формировании КМОП-структур применяются спейсеры — пристеночные разделители, выполняющие роль самосовмещенной маски при имплантации ионов в области истока и стока.

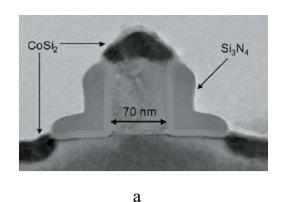

После очистки пластины на нее осаждают слой  $Si_3N_4$  (рис.1.10, <u>1.11</u>), который затем подвергают плазменному анизотропному травлению с остановкой на слое  $SiO_2$ . При этом  $Si_3N_4$  удаляется преимущественно с горизонтальных поверх-

ностей и остается на вертикальных стенках затвора. Образующиеся при этом спейсеры расширяют зону маскирования затвора.

| Эскиз | Операции                                                                                                                                                                                                                     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Осаждение слоя Si<sub>3</sub>N<sub>4</sub></li> </ul>                                                                                                                                                               |

|       | ■ Стравливание слоя Si <sub>3</sub> N <sub>4</sub> плазменным анизотропным травлением с остановкой на слое SiO <sub>2</sub>                                                                                                  |

|       | <ul> <li>Нанесение фоторезиста и вскрытие окон по форме областей <i>n</i>-типа</li> <li>Глубокое ионное легирование областей истокастока <i>n</i>-типа мышьяком</li> </ul>                                                   |

|       | <ul> <li>Удаление фоторезиста от предыдущей операции</li> <li>Нанесение фоторезиста и вскрытие окон по форме областей <i>p</i>-типа</li> <li>Глубокое ионное легирование областей истокастока <i>p</i>-типа бором</li> </ul> |

|       | <ul> <li>Удаление фоторезиста от предыдущей операции</li> <li>Быстрый термический отжиг легированных областей карманов</li> </ul>                                                                                            |

Рис. 1.10. Формирование спейсеров, областей истока и сток

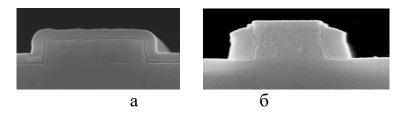

Рис. 1.11. Формирование спейсеров

а - осаждение слоя  $Si_3N_4$ , б – плазменное анизотропное травление

Заметим, что на этих же этапах происходит глубокое легирование зон контактов к соответствующим карманам.

С помощью фотолитографии оставляют закрытыми участки пластины с карманами n- типа, полностью открывая участки карманов p-типа. Далее следует ионное глубокое легирование мышьяком в областях истока-стока, при этом зона легирования ограничена не только поликристаллическим затвором и изоляцией  $SiO_2$  в мелких канавках, но и спейсерами.

Аналогично проводится следующая фотолитография для вскрытия окон на участках карманов n-типа. Глубокое ионное легирование бора формирует области истока-стока p-типа. После этого фоторезист удаляется, пластина подвергается очистке и быстрому термическому отжигу.

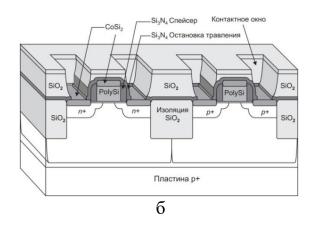

После глубокого ионного легирования с участием спейсеров сформированная структура имеет вид, показанный на рис. 1.12.

Рис. 1.12. КМОП структура после глубокого легирования стоков-истоков

# 1.1.2.5. Формирование контактов

Этапы формирования внутренних контактов к активным элементам КМОП структуры показаны на рис.1.13.

| Эскиз               | Операции                                                                                                                                                                                                                                          |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CoCoSi <sub>2</sub> | <ul> <li>Стравливание тонкого слоя SiO<sub>2</sub> со стока, истока, затвора</li> <li>Напыление тонкой пленки Со</li> <li>Быстрый термический отжиг до образования CoSi<sub>2</sub></li> </ul>                                                    |

|                     | <ul> <li>Селективное травления непрореагировавшего Со</li> <li>Второй быстрый термический отжиг для перевода CoSi<sub>2</sub> в фазу с малым сопротивлением</li> </ul>                                                                            |

|                     | <ul> <li>Осаждение тонкого стоп-слоя Si<sub>3</sub>N<sub>4</sub></li> <li>Осаждение толстого слоя SiO<sub>2</sub></li> </ul>                                                                                                                      |

|                     | <ul> <li>Химико-механическая планаризация толстого слоя SiO<sub>2</sub></li> <li>Покрытие тонким слоем SiO<sub>2</sub></li> </ul>                                                                                                                 |

|                     | <ul> <li>Формирование в фоторезисте окон к контактам в 1-м слое металла</li> <li>Травление толстого слоя SiO<sub>2</sub> до остановки на слое Si<sub>3</sub>N<sub>4</sub>.</li> <li>Травление тонкого слоя Si<sub>3</sub>N<sub>4</sub></li> </ul> |

Рис. 1.13. Формирование внутренних контактов

В качестве материала контактов к стоку и истоку используется силицид кобальта  $CoSi_2$ . Предварительно с областей истока и стока, а также с поверхности затвора удаляется тонкий слой  $SiO_2$ ().

Для этого пластина погружается в плавиковую кислоту HF, после чего она тщательно очищается. На поверхность пластины вакуумным напылением наносится тонкий слой Co. Проводится быстрый термический отжиг и в местах контакта кобальта с кремнием образуется силицид кобальта CoSi<sub>2</sub>

Непрореагировавший Со удаляется с помощью селективного травления, не действующего на силицид кобальта.

Второй быстрый термический отжиг (при более высокой температуре, чем первый) переводит  $CoSi_2$  из фазы с высоким в фазу с малым сопротивлением. Именно в этой фазе силицид кобальта контактирует с истоком, стоком и затвором.

Пластины очищаются, последовательно наносятся тонкий стоп-слой  $Si_3N_4$  и слой диэлектрика перед нанесением первого слоя металлизации – PMD (*pre-metal dielectric*).

В качестве такого диэлектрика обычно применяют борофосфоросиликатное стекло (БФСС - BPSG) — двуокись кремния  $SiO_2$  с содержанием от 2 до 6 весовых процентов бора и фосфора. БФСС обычно формируется химическим осаждением из паровой фазы при температуре 500-700 °C а затем отжигается при температуре 800-1000 °C.

Химико-механической полировкой проводится планаризация поверхности пластин для обеспечения высокого разрешения фотолитографии. Пластины тщательно очищаются, их поверхности покрывается тонким слоем SiO<sub>2</sub>.

Для создания окон к контактам проводят фотолитографию и через окна в фоторезисте проводят плазменное травление слоя PMD до остановки на слое  $Si_3N_4$ . Последующее травление тонкого слоя  $Si_3N_4$  формирует окна к контактам.

Образующаяся в результате структура с контактами из силицида кобальта  $CoSi_2$  показана на рис. 1.14. Отметим, что для создания контактов могут использоваться и другие силициды, например,  $TiSi_2$

Рис. 1.14. КМОП структура с внутренними контактами

а - контакты из силицида кобальта  $CoSi_2$ , б – окна к внутренним контактам

## 1.1.2.6. Формирование металлических проводников: 1-й слой металла

Формирование металлических проводников начинается с напыления тонкого слой титана (Ті), на который методом осаждения из паровой фазы наносится толстый слой вольфрама (W) (рис.1.15).

Вольфрам — это материал, из которого будут формироваться межслойные соединения — микропереходы - между слоями металлизации. Однако у него очень плохая адгезия к  $SiO_2$ . Титан, в отличие от вольфрама, обладает отличной адгезией к  $SiO_2$  и поэтому используется в качестве материала промежуточного слоя.

Слой подвергается планаризации - химико-механической полировкой снимается до уровня  $SiO_2$ . Режимы полировки подбираются так, чтобы скорость удаления W была во много раз больше, чем  $SiO_2$ . Поэтому на слое  $SiO_2$  планаризация завершается. Пластина очищается и на нее вакуумным напылением последовательно наносятся:

- адгезионный слой Ті,

- барьерный слой ТіN,

- слой металлизации медно-алюминиевый сплав AlCu,

- слой Ті для предотвращения образования AlN

- антиотражающий слой TiN.

| Эскиз | Операции                                                                                                                                                                                                                                                                                     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Напыление тонкого адгезионного слоя Ті</li> <li>Осаждение толстого слоя W – основы межслойных соединений</li> </ul>                                                                                                                                                                 |

|       | <ul> <li>Химико-механическая планаризация вольфрама</li> </ul>                                                                                                                                                                                                                               |

|       | <ul> <li>Напыление тонкого адгезионного слоя титана (Ті)</li> <li>Напыление тонкого барьерного слоя ТіN</li> <li>Напыление межслойной металлизации AlCu</li> <li>Напыление тонкого слоя Ті для предотвращения образования AlN</li> <li>Напыление тонкого антиотражающего слоя ТіN</li> </ul> |

|       | <ul> <li>Нанесение фоторезиста и вскрытие окон по форме контактов в 2-ом слое металла</li> <li>Травление пакета металлических слоев</li> <li>Удаление фоторезиста</li> </ul>                                                                                                                 |

Рис. 1.15. Формирование металлических межсоединений в 1-ом слое металла

Слой Ті наносится поверх AlCu для предотвращения образования во время напыления ТіN нитрида алюминия AlN, обладающего очень высоким электрическим сопротивлением.

Слой TiN на поверхности AlCu служит антиотражающим покрытием во время фотолитографии по металлической пленке.

Далее фотолитографией вскрываются окна в фоторезисте, соответствующие топологии металлических микропереходов первого уровня и проводится последовательное травление пакета металлических слоев до слоя  $SiO_2$ .

После удаления фоторезиста получается структура, показанная на рис. 1.16.

Рис. 1.16. КМОП структура с межсоединениями в 1-ом слое металла

## 1.1.2.7. Формирование металлических проводников: 2-й слой металла

Формирование второго уровня металлизации начинается с создания слоя диэлектрика между уровнями металлизации (*inter metal dielectric - IMD*) (рис. 1.17).

Пластины очищаются, осаждением из газовой фазы наносятся слой нелегированного силикатного стекла -  $SiO_2$ . Химико-механической полировкой проводится планаризация поверхности пластин, они тщательно очищаются и поверхность планаризованного слоя покрывается тонким слоем  $SiO_2$ .

| Эскиз | Операции                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Осаждение толстого межслойного SiO<sub>2</sub></li> <li>Химико-механическая планаризация SiO<sub>2</sub></li> <li>Покрытие тонким слоем SiO<sub>2</sub></li> </ul>                                                                                                                                                                                                                                               |

|       | <ul> <li>Нанесение фоторезиста и вскрытие окон по форме контактов в 2-ом слое металла</li> <li>Травление межслойного SiO<sub>2</sub></li> </ul>                                                                                                                                                                                                                                                                           |

|       | <ul> <li>Удаление фоторезиста</li> <li>Напыление тонкого адгезионного слоя Ті</li> <li>Осаждение толстого слоя W – основы межслойных соединений</li> <li>Химико-механическая планаризация W</li> </ul>                                                                                                                                                                                                                    |

|       | <ul> <li>Напыление тонкого адгезионного слоя Ті</li> <li>Напыление тонкого барьерного слоя ТіN</li> <li>Напыление тонкого слоя металлизации AlCu</li> <li>Напыление тонкого слоя Ті для предотвращения образования AlN</li> <li>Напыление тонкого антиотражающего слоя ТіN</li> <li>Нанесение фоторезиста и вскрытие окон по форме контактов в 2-ом слое металла</li> <li>Травление пакета металлических слоев</li> </ul> |

Рис. 1.17. Формирование металлических межсоединений во 2-м слое металла

Проводится очередная фотолитография — наносится фоторезист, в нем вскрываются окна по форме контактов в 2-ом слое металла. Через окна в фоторезисте ведется травление межслойного  $SiO_2$ .

Далее повторяются операции, использованные при формировании 1-го уровня металлизации: нанесение слоев Ti, TiN, AlCu, Ti, TiN.

Фотолитографией вскрываются окна в фоторезисте, соответствующие топологии металлических микропереходов второго уровня и проводится последовательное травление пакета металлических слоев до слоя  $SiO_2$ .

После удаления фоторезиста получается структура (рис.1.18), весьма напоминающая структуру на рис. 1.16 после формирования межсоединений в 1-ом слое металла. Последовательность операций для формирования 2-го слоя металлизации может быть использована для получения 3-го, 4-го и последующих слоев.

Рис. 1.18. Многослойные металлические межсоединения  $a-\phi$ ото,  $\delta-$ схема

После формирования последнего слоя металлизации проводится нанесение слоя  $SiO_2$  и его планаризация. В завершение обычно наносится пассивирующий слой  $Si_3N_4$ , который предохраняет структуру от влаги и загрязнений.

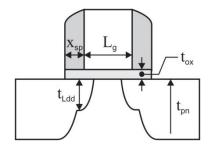

## 1.1.2.8. Масштабирование КМОП микросхем

Ключевым геометрическим параметром МОП структур является длина затвора транзистора  $L_g$ , которая за последние 30 лет уменьшилась в 200 раз - с 10 мкм в начале 70-х годов до 65 нм в наши дни. Уменьшение длины затвора определяет изменение других параметров транзистора (см. табл.1.2).

Таблица 1.2

| Параметр                                                            | Коэффици-<br>ент<br>масштаба | Значения |          |  |

|---------------------------------------------------------------------|------------------------------|----------|----------|--|

|                                                                     |                              | Исходные | Конечные |  |

| Длина затвора, $L_g$                                                | 1/k                          | 90 нм    | 65 нм    |  |

| Рабочее напряжение                                                  | 1/k                          | 1 B      | 0,7 B    |  |

| Плотность компонентов                                               | $k^2$                        | 1x       | 2x       |  |

| Потребляемая мощность                                               | $1/k^2$                      | 1x       | 0,5x     |  |

| Плотность                                                           | 1                            | 1        | 1        |  |

| Время задержки сигнала                                              | 1/k                          | 1x       | 0,7x     |  |

| Произведение времени за-<br>держки сигнала на мощность<br>рассеяния | $1/k^3$                      | 1x       | 0,4x     |  |

| Функциональная производительность                                   | k <sup>3</sup>               | 1x       | 2,7x     |  |

Так, при коэффициенте масштаба k = 1,4, что соответствует переходу на следующий уровень технологии, длина затвора уменьшается с 90 до 65 нм.

При этом рабочее напряжение, необходимое для сохранения прежнего значения напряжения поля в МОП структуре, уменьшится с 1 до 0,7 В.

Плотность размещения компонентов, т.е. количество МОП структур на единице площади, при k=1,4 увеличивается практически в 2 раза. Это дает экономию в стоимости производства в 1,3-1,5 раз с учетом того, что возрастает сложность применяемого оборудования и увеличивается его номенклатура.

Потребляемая мощность при заданном коэффициенте масштаба уменьшается вдвое, при этом плотность энерговыделения при неизменном напряжении электрического поля остается на прежнем уровне.

Время задержки сигнала уменьшается в k = 1,4 раза, а произведение времени задержки сигнала на мощность рассеяния (критерий качества, оценивающий баланс между скоростью прохождения сигнала и рассеиваемой мощностью) уменьшается в 2,5 раза.

Наконец, изменяется и функциональная производительность — еще один комплексный критерий качества, который равен произведению числа затворов МОП структур на тактовую частоту, деленному на потребляемую мощность. Значение данного параметра в рассматриваемом случае увеличивается в  $k^3$  раз.

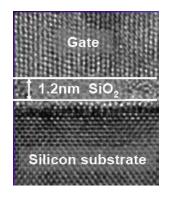

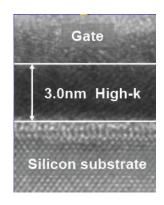

Заметим, что для сохранения функциональных свойств МОП структуры при уменьшении длины затвора должны быть также уменьшены и другие ее размеры (рис. 19). Многолетний опыт применения масштабирования позволил выработать рекомендации по коэффициентам пропорциональности для отдельных элементов структур. Например, разработчики фирмы Intel при коррекции толщины подзатворного оксида  $t_{ot}$  используют соотношение:

$$t_{ox} = L_g / 45.$$

Аналогичные соотношения приняты для геометрических параметров:

- глубина p-n перехода:  $t_{pn} \approx 0.8 L_g$ ,

- глубина слаболегированной области (Ldd):  $t_{Ldd} \approx 0, 4L_g$ ,

- ширина спейсера:  $x_{sp} \approx 0.5L_g$

Рис. 1.19. Размеры МОП структуры

Рассмотренный пример показывает, что масштабирование ведет к существенному улучшению рабочих характеристик МОП структур.

Поэтому тенденция к уменьшению размеров интегральных микросхем наблюдается на всем протяжении развития микроэлектроники, в развитии которой четко прослеживаются *временные циклы*, характеризующие ее переход на новый *уровень технологии*. Наличие таких циклов предсказал еще в 1965 г. один из основателей фирмы *Intel* Гордон Мур.

Обычно для оценки современного уровня микроэлектронной технологии используют параметры наиболее распространенных микросхем - микропроцессоров и схем памяти. В соответствии с современной версией эмпирического закона Мура функциональные возможности схем памяти (объем или число ячеек памяти) и микропроцессоров (число транзисторов и быстродействие) удваиваются каждые два года.

Количественно уровень технологии микроэлектроники определяется *топо- погической нормой*. Этот параметр различается по физическому смыслу для различных изделий микроэлектроники. Так, до начала 90-х годов самыми передовыми в технологическом плане изделиями были схемы памяти (рис. 1.20, а).

Рис. 1.20. Интегральная микросхема

а - общая топология, б - дорожки адресных шин, в — металлические контакты первого уровня, г - линия, промежуток и шаг регулярной структуры

В них адресные и разрядные шины (bit lines, word lines) формируются в виде регулярных структур – решеток (рис. 1.20, б). Конструкция современных интегральных схем предусматривает, как правило, многослойную металлизацию. Решетка контактов, непосредственно примыкающих к активным элементам схемы (первый уровень металлизации), имеет минимальный шаг в данной микросхеме (рис. 1.20, в).

Поэтому *полушаг* решетки адресных дорожек с контактами первого уровня металлизации традиционно используется в качестве *топологической нормы*, характеризующей *плотность упаковки элементов на кристалле*.

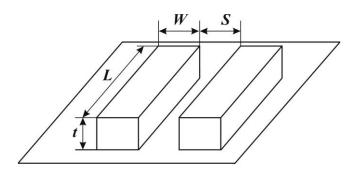

Заметим, что шаг P решетки (pitch) складывается из ширины L дорожки (line) и промежутка S (space) между ними (рис. 1.20, г). В случае, когда L=S, полушаг ( $half\ pitch$ ) этой решетки равен ширине дорожки (топологической линии.

Полушаг в полной мере характеризует *плотность упаковки элементов* регулярной структуры. В структурах микропроцессоров, технология которых в последние десятилетия развивается ускоренными темпами, в качестве топологической нормы также может использоваться полушаг регулярных структур.

Его уменьшение, например, с 180 до 130 нм при сохранении функциональных возможностей микропроцессора уменьшает его площадь на 45% (рис. 1.21).

Оглавление

Рис. 1.21. Влияние топологических норм на габариты ИС а - уменьшение с 180 до 130 нм, б – уменьшение с 130 до 90 нм.

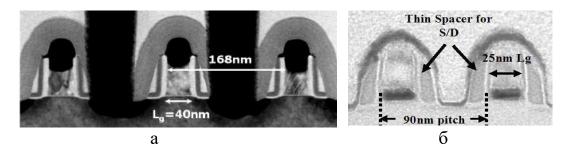

Однако в данном случае промежутки в таких структурах обычно существенно превышают размеры отдельных элементов (рис. 1.22).

Рис. 1.22. Критические размеры в МОП транзисторе а - шаг 168 нм, длина затвора 40 нм, б – шаг 90 нм, длина затвора 25 нм.

Поэтому в производстве микропроцессоров в качестве параметра уровня технологии чаще используют *минимальный размер элемента* (*CD – critical dimension*). Им обычно является длина затвора МОП транзисторов, на рис. 3 она составляет, соответственно, 40 и 25 нм. Требования к размерной точности микропроцессоров и совмещаемости не превышают единиц нанометров (табл. 1.3.).

Состояние и прогноз развития параметров микропроцессоров Таблица 1.3

| Год выпуска                                    | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 |

|------------------------------------------------|------|------|------|------|------|------|------|------|------|

| Полушаг, нм                                    | 65   | 57   | 50   | 45   | 40   | 36   | 32   | 28   | 25   |

| Контакты в резисте, нм                         | 84   | 73   | 64   | 56   | 50   | 44   | 39   | 35   | 31   |

| Контакты после травления, нм                   | 77   | 67   | 58   | 51   | 45   | 40   | 36   | 32   | 28   |

| Совмещаемость (3 $\sigma$ ), нм                | 13,0 | 11,3 | 10,0 | 9,0  | 8,0  | 7,1  | 6,4  | 5,7  | 5,1  |

| Длина затвора в резисте,<br>нм                 | 84   | 73   | 64   | 56   | 50   | 44   | 39   | 35   | 31   |

| Длина затвора после травления, нм              | 77   | 67   | 58   | 51   | 45   | 40   | 36   | 32   | 28   |

| Размерная погрешность после травления (3σ), нм | 2,6  | 2,3  | 2,1  | 1,9  | 1,7  | 1,5  | 1,3  | 1,2  | 1,0  |

#### 1.1.3. Приложения

## П.1.1. Параметры металлических межсоединений

В рассматриваемом примере выполненные в первом слое металла межсоединения объединяют активные элементы КМОП структуры в схему инвертора.

В интегральных схемах более высокого уровня сложности требуются дополнительные слои металлизации, причем их число постоянно возрастает по мере увеличения количества элементов схемы до сотен тысяч и миллионов единиц.

Для обеспечения высокой тактовой частоты в логических схемах, например, микропроцессорах, время задержки при прохождении сигнала должно быть минимальным.

В свою очередь, время резистивно-емкостной задержки  $au_{RC}$  распространения сигнала в проводящих линиях определяется постоянной времени соединительной линии, зависящей от ряда ее параметров:

$$\tau_{RC} = \rho_{Me} \frac{L}{W \cdot t_{Me}} \cdot k \varepsilon_0 \frac{L \cdot W}{t_{Ox}} = \rho_{Me} \frac{k \varepsilon_0 L^2}{t_{Me} t_{Ox}}$$

(II1.1)

где  $\rho_{\mathit{Me}}$ ,  $\mathit{L}$ ,  $\mathit{W}$ ,  $\mathit{t}_{\mathit{Me}}$ — удельное сопротивление, длина, ширина и толщина проводников,

$t_{\mathit{Ox}}$  — толщина межслойного диэлектрика,

$\varepsilon_0$  — диэлектрическая проницаемость вакуума.

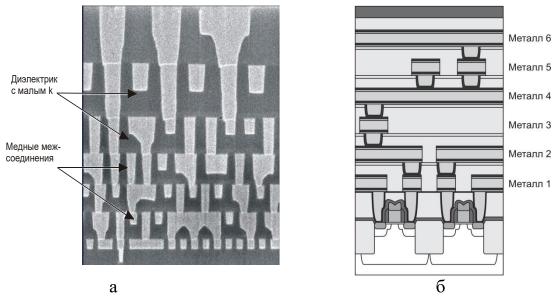

Как видно из вышеприведенного уравнения, резистивно-емкостная задержка зависит от квадрата длины проводника. Применение многослойной металлизации позволяет при трассировке проводников существенно уменьшить их длину, по сравнению с одно- или двухслойной металлизацией. В реальных интегральных схемах повсеместно используется шестислойная металлизация, апробируются структуры с металлизацией на 7-9 уровнях.

Кроме того, все более широко применяются межслойные диэлектрики с малым значением диэлектрической постоянной k.

Шестислойная металлизация формируется по определенным правилам: пер-

вые два слоя, локально соединяющие элементы структур и сами структуры между собой, имеют минимальный шаг проводников. В третьем и четвертом слоях шаг и длина проводников увеличиваются, в пятом и шестом слоях проводники с еще большим шагом и длиной используются для подвода питания и межсоединений.

Металлические проводники верхних слоев выполняются достаточно толстыми, чтобы уменьшить их сопротивление, в то время как проводники нижних слоев должны быть предельно тонкими — в толстых металлических пленках трудно вытравить узкие полосы с малым шагом.

На рис. 1.17 показана геометрия проводников и их характерные размеры: ширина проводника W, зазор S, толщина t, длина L, отношение толщине к ширине (Aspect Ratio, AR=t/W). Размеры проводников для микропроцессора фирмы Intel по 180 нм технологии представлены в таблице 1.2.

Рис. 1.17. Размеры проводников

Таблица 1.2

## Параметры металлических проводников в многослойной металлизации

| Слой | t, HM | <i>W</i> , нм | <i>S</i> , нм | AR  |

|------|-------|---------------|---------------|-----|

| 6    | 1720  | 860           | 860           | 2,0 |

| 5    | 1600  | 800           | 800           | 2,0 |

| 4    | 1080  | 540           | 540           | 2,0 |

| 3    | 700   | 320           | 320           | 2,2 |

| 2    | 700   | 320           | 320           | 2,2 |

| 1    | 480   | 250           | 250           | 1,9 |

Как следует из уравнения П1.1, резистивно-емкостная задержка распро-

странения сигнала в проводящих линиях определяется сопротивлением металлических проводников и диэлектрическими свойствами межслойных изоляторов.

В схемах с полушагом менее 180 нм алюминий в качестве материала проводников начинает заменяться медью, имеющей меньшее удельное сопротивление. Одновременно начинается применение материалов с малым значением диэлектрической постоянной (low-k) в качестве материалов межслойных изоляторов.

В конечном счете, оба этих решения все более широко используются совместно для уменьшения времени задержки в межсоединениях.

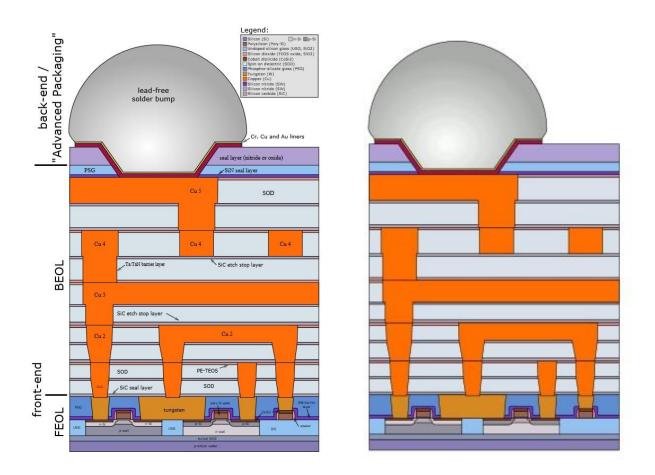

## П.1.2. Особенности формирования медных межсоединений.

Применение в качестве материала проводников меди сопряжено с рядом проблем. Так, медь практически не поддается плазменному травлению, зато легко диффундирует через  $SiO_2$  и Si, привнося загрязнения и ухудшая характеристики схем.

Для решения этих проблем разработана технология, которая позволяет получать медные проводники заданной топологии, обеспечивая при этом барьерные слои, предотвращающие загрязнение кремния. Эта технология, получившая название damascene (инкрустация), применима при создании микрорельефов заданной топологии практически из любых материалов, поддающихся химикомеханической полировке – планаризации.

Метод точно соответствует своему названию — в нем литографии и последующему травлению подвергается пленка SiO (рис. 1.20)<sub>2</sub>, затем в созданный микрорельеф осаждается металл, при этом конфигурация металлического рельефа формируется без травления, за счет снятия излишков меди при планаризации.

Используется также модификация этой технологий — двойная инкрустация (*dual damascene*). В этом методе сквозное отверстие для межсоединения (*via*) и топология медных проводников формируются одновременно (рис.1.21).

| Эскиз | Операции                                             |

|-------|------------------------------------------------------|

|       | Осаждение толстого слоя SiO <sub>2</sub>             |

|       | Нанесение фоторезиста и фотолитография               |

|       | Травление SiO <sub>2</sub><br>Удаление фоторезиста   |

|       | Осаждение слоя металла                               |

|       | Планаризация слоя металла до уровня SiO <sub>2</sub> |

Рис. 1.20. Технология *damascene* (инкрустация)

После очистки на пластину последовательно наносится пакет слоев:  $SiO_2$ ,  $Si_3N_4$  и снова  $SiO_2$ . Первый слой  $SiO_2$  — это межслойный диэлектрик между слоями металлизации. Слой  $Si_3N_4$  служит стоп-слоем при последующем травлении  $SiO_2$ , делая процесс управляемым. Во втором слое  $SiO_2$  формируются металлические межсоединения заданной топологии.

Проводится первая фотолитография и через окна в фоторезисте травятся отверстия для сквозных межсоединений — сначала в  $SiO_2$  до остановки на слое  $Si_3N_4$ , а затем и сам слой  $Si_3N_4$ . После этого фоторезист удаляется.

Вторая фотолитография формирует в фоторезисте окна с конфигурацией металлических проводников. Через эти окна травится верхний слой  $SiO_2$  до остановки на стоп-слое  $Si_3N_4$ , и одновременно через ранее вскрытые окна в этом слое протравливаются отверстия для сквозных межсоединений.