**EPCI European Passive Components Institute**

www.passive-components.eu

EPCI | Bringing European Passive Professionals Together

# **CAPACITORs and RESISTORs**

## **MOUNTING GUIDE SURVEY**

## **BASED ON COMMERCIAL MANUFACTURERS' PUBLIC DOCUMENTS**

Tomáš Zedníček, Ph.D.

EPCI, European Passive Components Institute T.G.Masaryka 477, 563 01 Lanškroun, Czech Republic e-mail: tom@passive-components.eu

Version: 2.0

Issue: July 2018

## Content

| 1. | PREF  | ACE   |                                                                         | 3  |

|----|-------|-------|-------------------------------------------------------------------------|----|

| 2. | INTR  | ODU   | CTION                                                                   | 4  |

| 3. | INDU  | JSTRY | MOUNTING AND COMPONENT HANDLING SPECIFICATION REVIEW                    | 5  |

| 4. | MOL   | INTIN | IG GUIDE GENERAL CONCEPTS                                               | 6  |

|    | 4.1.  | Μου   | NTING TECHNIQUES OVERVIEW                                               | 6  |

|    | 4.1.1 |       | IR reflow soldering                                                     |    |

|    | 4.1.2 |       | Wave Soldering                                                          |    |

|    | 4.1.3 |       | Vapour Phase Soldering                                                  |    |

|    | 4.1.4 | !.    | Wire Bonding                                                            | 10 |

|    | 4.1.5 |       | Adhesive Bonding                                                        | 11 |

|    | 4.1.6 | i.    | Hand Soldering                                                          | 11 |

|    | 4.1.7 |       | PCB Embedding                                                           | 12 |

|    | 4.2.  | Сом   | MON SOLDERING PROCESS ISSUES                                            | 13 |

|    | 4.2.1 |       | Oxidisation                                                             | 13 |

|    | 4.2.2 |       | Component displacement                                                  | 14 |

|    | 4.2.3 |       | Outgassing                                                              | 14 |

|    | 4.2.4 |       | Sulphur Contamination                                                   | 15 |

|    | 4.3.  | GENE  | RAL MEASURES TO ENHANCE COMPONENTS' SOLDERING AND MOUNTING CAPABILITIES | 15 |

| 5. | COM   |       | ENT MANUFACTURERS MOUNTING GUIDE SURVEY                                 | 16 |

| э. | CON   |       |                                                                         |    |

|    | 5.1.  |       | RD DESIGN AND COMPONENT PRE-ASSEMBLY PREPARATION                        |    |

|    | 5.2.  | Сом   | PONENT SPACING                                                          | 21 |

|    | 5.3.  |       | PONENT HANDLING                                                         |    |

|    | 5.4.  | Ріска | & PLACE                                                                 | 22 |

|    | 5.5.  | SOLD  | ERING                                                                   | 24 |

|    | 5.5.1 | -     | Flux                                                                    | 25 |

|    | 5.5.2 |       | Preheat                                                                 |    |

|    | 5.5.3 |       | Cooling                                                                 |    |

|    | 5.5.4 | -     | Solder Joint Quality                                                    |    |

|    | 5.6.  | CLEAR | NING                                                                    | 26 |

|    | 5.7.  |       | Solder Handling                                                         |    |

|    | 5.8.  |       | COATING, POTTING AND MOLDING                                            |    |

|    | 5.9.  | PCB   | Cut and Cropping                                                        | 28 |

|    | 5.10. | -     | STORAGE                                                                 |    |

|    | 5.11. | Rewo  | DRK                                                                     |    |

|    | 5.11. | 1.    | Solder Iron Rework                                                      |    |

|    | 5.11. | 2.    | Spot Heater Rework                                                      | 31 |

|    | 5.12. | Сом   | PONENT STORAGE                                                          | 32 |

|    | 5.13. | RE-LI | FE                                                                      | 32 |

| 6. | REFE  | RENC  | ES                                                                      | 33 |

| 7. | ACK   | NOWI  | LEDGEMENT                                                               | 33 |

## 1. Preface

The aim of this survey is to collect and summarise mounting recommendations of **publicly** available information from capacitor and resistor **commercial component manufacturers**.

The survey aim is to **collect the manufacturer's recommendations and good tips for capacitors and resistor mounting BEYOND the industry standards**. The survey doesn't aim to provide a complete mounting procedure guidelines as part of specific industrial requirement and standards.

Capacitor and Resistor Manufacturers Public Sources Included in the survey:

#### **Capacitor Manufacturers:**

- AVX

- Cobham Microwave

- Exxelia

- Kemet

- Murata

- Nichicon

- Nippon Chemicon

- Taiyo-Yuden

- TDK

- Semco

- Panasonic

- Vishay

- Walsin

- Yageo

#### **Resistor Manufacturers:**

- Ampcontrol

- Arcol

- Cressall Resistors

- HVR Pentagon

- Isabellenhütte Heusler

- Japan Resistor Manufacturing

- KOA Speer

- Murata

- Ohmite

- Panasonic

- Rohm

- TE Connectivity

- Telema Precision Resistor Company

- Vishay (USA)

The mounting guide survey was prepared under European Space Agency ESA contract with European Passive Components Institute on passive components support.

## 2. Introduction

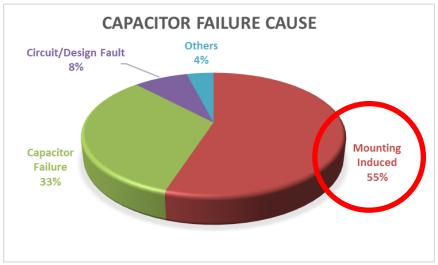

Fig 1. capacitor failure cause source: [2] EPCI based on end user survey

Mounting related induced failures are the number one reason (over 55%) for the field application capacitor failure causes according to a EPCI end customer survey – see Fig.1. The capacitor component failures itself represents "just" 33% of the root failure causes. Thus, a careful evaluation of mounting guidelines and follow up in real assembly processes per the component manufacturers' recommendations shall be considered as a critical characteristic. This mounting guide survey report summarises recommendations of ESCC QPL capacitor and resistor technology (including both QPL and other commercial manufacturers) and present some recommendations, tip & tricks for the best mounting practice published by component manufacturers. Space requirements, as specified in ECSS standards, are not included in this guide.

Board mounting soldering processes itself shall be adapted to contradictory requirements. On one hand, a certain minimum time in the molten solder to get a good wetting is needed and on the other hand, as short exposure to the molten solder as possible to minimize any risk of damage on component. The following items to be considered for selection of the proper mounting technique and its parameters:

- many times mounting process is "the worst electrical and mechanical stress in the component's life"

- thermal stress may damage parts by excessive heat

- thermal stress may cause issues due to CTE mismatch

- degradation by thermally driven wear out mechanisms diffusion, migration, increase of chemical activity ...

- component history (packaging, transport) may play a key role

- strong absorbed humidity and oxidisation impact

- pre-tinning and re-soldering (SnPb solder dip) requirements

- rework option and conditions

- temperature exposure is directly proportional to the post reflow failures and ppm life failures

- PCB construction, number of layers, technology used, required volume and soldering process repeatability

- handling of components (manual/pick & place) and PCB (mechanical shock, vibration, rack/holder loading, support pins use, screwing position/sequence/force, ...)

## 3. Industry Mounting and Component Handling Specification Review

The following is a list of most common soldering and mounting standards used and referred by passive component manufacturers in their mounting guide specifications:

- **EIA/IPC/JEDEC J-STD-002E** Solderability Tests for Component Leads, Terminations, Lugs, Terminals and Wires

- JESD22-B102E Solderability

- **IPC/JEDEC J-STD-020E** Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices

- **IPC/JEDEC J-STD-033C** Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices

- ECIA/IPC/JEDEC J-STD-075 Classification of Passive and Solid State Devices for Assembly Processes

- **BS CECC 00802** Harmonized system of quality assessment for electronic components. Guidance document: CECC Standard method for the specification of surface mounting components (SMDs) of assessed quality

- EN NF 61192 Workmanship Requirements For Soldered Electronic Assemblies, AFNORM

- **EN 61760-1:2006** Surface mounting technology Part 1: Standard method for the specification of surface mounting components (SMDs)

- IPC/JEDEC-EIA-625 Requirements For Handling Electrostatic-Discharge-Sensitive (ESDS) Devices

- IPC-2221 Generic Standard on Printed Board Design

- IPC-SM-782 Surface Mount Design and Land Pattern Standard

## 4. Mounting Guide General Concepts

#### 4.1. Mounting Techniques Overview

#### 4.1.1. IR reflow soldering

IR infrared "convection" reflow is commonly used in commercial large volume SMD components mounting process. The main differences in reflow soldering processes and oven types lie in heat transfer methods - radiation, conduction, convection and condensation. In fact, all heat transfers are used in modern reflow ovens. The heat is applied from above, below, or all directions dependent on the equipment being used. In classical infrared "radiation" reflow ovens, several ceramic heaters are transferring the heat to the assemblies, moving through the oven on a conveyor belt, by radiation. The limitation was the risk of oxidation and overheating. Nevertheless, the use of fans to help the transfer efficiency by convection minimized highly this issue. Nowadays, the reflow ovens are called "convection ovens" because the heat is mostly transferred by forced air circulation; nitrogen may be used to help wettability in addition.

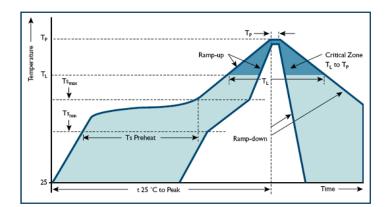

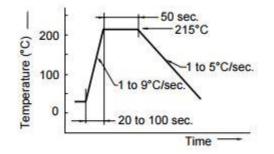

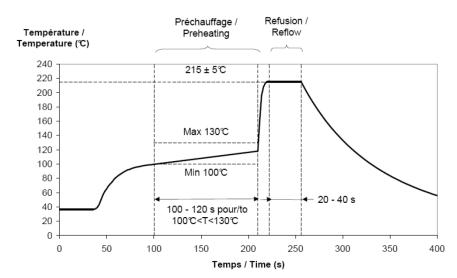

Components are picked from a tape and placed on PCB pads covered by a solder paste. The PCB with components are then placed on a belt that passes through a temperature reflow profile as shown on example figure 2. below. The zones can be split into a four main phases – preheat, peak ramp up, time above liquidus and ramp down time. See classification of reflow profiles as per J-STD-020 in Figure 2. below.

| Classification of Reflow Profiles                                                                                                                                                                            |                                 |                                          |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------|--|--|--|

| Profile Feature                                                                                                                                                                                              | Sn – Pb Eutectic Assembly       | Lead (Pb)-Free Assembly<br>(e.g. SnAgCu) |  |  |  |

| Average ramp-up rate (T <sub>(Smax.)</sub> to T <sub>P</sub> )                                                                                                                                               | 3 °C/s maximum                  |                                          |  |  |  |

| <ul> <li>Preheat</li> <li>Temperature minimum (T<sub>S(min.)</sub>)</li> <li>Temperature maximum (T<sub>S(max.)</sub>)</li> <li>Time (T<sub>S(min.)</sub> to T<sub>S(max.)</sub>) (t<sub>S</sub>)</li> </ul> | 100°C<br>150°C<br>60 s to 120 s | 150°C<br>200°C<br>60 s to 180 s          |  |  |  |

| Time maintained above • Temperature minimum (T <sub>L</sub> ) • Time (T <sub>L</sub> )                                                                                                                       | 183°C<br>60 s to 150 s          | 217<br>60 s to 150 s                     |  |  |  |

| Minimum peak temperature (T <sub>P(min.)</sub> )                                                                                                                                                             | 215°C                           | 235°C                                    |  |  |  |

| Recommended peak temperature (T <sub>P</sub> )                                                                                                                                                               | 235°C                           | 250°C                                    |  |  |  |

| Maximum peak temperature (T <sub>P(max.)</sub> )                                                                                                                                                             | 260°C                           | 260°C                                    |  |  |  |

| Time within 5°C of actual peak temperature (tp)                                                                                                                                                              | 10 s to 40 s                    | 20 s to 40 s                             |  |  |  |

| Ramp-down rate                                                                                                                                                                                               | 6°C/s maximum                   | 6°C/s maximum                            |  |  |  |

| Time 25°C to peak temperature                                                                                                                                                                                | 6 min maximum                   | 8 min maximum                            |  |  |  |

Fig 2. Typical IR reflow profile with key parameters and classification – refer to IPC/JEDEC J-STD-020E

The first **preheat** phase allow activation of the solder paste flux to clean and de-oxidize the finish of the PCB and components to promote a good wetting. The preheat is also critical to raise the temperature of the PCB and component as uniformly as possible to limit the difference in temperature at solder joint level between different components. The preheat important function from the component perspective is removal of moisture residuals\*. The preheat time at temperatures over water boiling temperature is important to provide sufficient time to release moisture even from deep structures and slow moving mechanisms. On the other hand, too long exposure to higher temperature may accelerate some degradation mechanisms and induce some damage to the components.

\* Note: Removal of moisture from PCB and component shall be done before assembly following the JEDEC J-STD-033 for industry reference. Despite the moisture removal, some level of residuals may still present inside of deep states inside of components.

The solder paste is activated during the ramp up phase. The peak temperature, time above a certain temperature (defined by the solder paste melting point) and temperature gradient are the other critical reflow parameters that on one side guarantee a reliable soldering and on the other hand, it may induce some (over)stress to the component. Usually, the peak temperature is set about 20-30°C above the solder paste melting point to provide enough margin for good soldering characteristics in real conditions considering the actual IR reflow oven load (empty vs fully loaded belt), PCB layout, temperature shielding behind larger components, set-up temperature variability (middle oven vs belt edge), set temperature stability etc. The IPC/JEDEC J-STD 020 standard that is followed by majority of industry is classifying peak temperature in relation to the packaging thickness and volume – see Fig. 3 below.

| Table 4-1 SNPb Eutectic Process - Classification Temperatures $(T_c)$ |                        |                        |  |  |  |

|-----------------------------------------------------------------------|------------------------|------------------------|--|--|--|

|                                                                       | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |  |  |  |

| Package Thickness                                                     | <350                   | ≥350                   |  |  |  |

| <2.5 mm                                                               | 235 °C                 | 220 °C                 |  |  |  |

| ≥2.5 mm                                                               | 220 °C                 | 220 °C                 |  |  |  |

-----

(**T**)

|   | Table 4-2 Pb-Free Process - Classification Temperatures ( $T_c$ ) |                                |                                      |                                 |  |  |  |

|---|-------------------------------------------------------------------|--------------------------------|--------------------------------------|---------------------------------|--|--|--|

|   | Package<br>Thickness                                              | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350 - 2000 | Volume mm <sup>3</sup><br>>2000 |  |  |  |

| Γ | <1.6 mm                                                           | 260 °C                         | 260 °C                               | 260 °C                          |  |  |  |

| Γ | 1.6 mm - 2.5 mm                                                   | 260 °C                         | 250 °C                               | 245 °C                          |  |  |  |

| Г | >2.5 mm                                                           | 250 °C                         | 245 °C                               | 245 °C                          |  |  |  |

| Table 4-2 Pb-Free Process - Class | sification Temperatures $(T_c)$ |

|-----------------------------------|---------------------------------|

|-----------------------------------|---------------------------------|

Fig.3. SnPb and Pb-free package temperature classification, as per IPC/JEDEC J-STD-020E

Attention has to be also paid to the number of allowed reflow cycles. J-STD-020 calls for two (two PCB sides) or three reflows (two PCB sides and rework) that components have to survive during the mounting. Nevertheless, this number of cycles may not be achievable by some technologies such as aluminium or film capacitors, thus please always check the manufacturer specification.

The peak temperature gradient, however can be the most critical reflow parameter (even sometimes more critical than peak temperature itself) for many components. Despite the correct preheat zone water removal is present, still some deep moisture residuals can quickly evaporate during the peak temperature ramp up. This may cause a "pop corning" effect with subsequent cracking in the component structure/packaging resulting in imminent parametric, catastrophic short/open circuit or impact to the overall component life time and environmental robustness. The general recommendation is to keep the peak temperature gradient below 2.5°C/s.

The PCB and solder is cooled during **ramp down** phase. Natural cooling rate is generally recommended; attention has to be paid when forced cooling is used as some components specify the **maximum cool down temperature gradient** (such as MLCC capacitors).

#### Commonly used solder paste types:

SnPb

- Sn63Pb37 the most common type, melting point 183°C, peak reflow temp ~ 220°C

- Pb content = ROHS Issues

- used in specific applications (defence, space) to avoid tin whisker issues

LeadFree

- most common SnAgCu solder, melting point ~ 217°C, peak reflow temp ~ 245 to 260°C

- JEDEC standards for small components: 260°C, 30sec peak, 3x reflow for large components: 245-255°C

Important Note: Some components such as PET SMD film capacitors are not designed to withstand a lead-free reflow cycle.

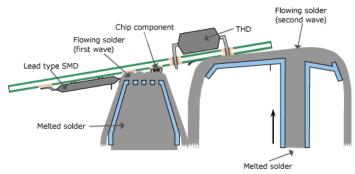

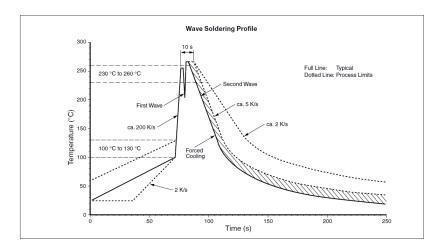

#### 4.1.2. Wave Soldering

The wave soldering process is often used for old designs or/and pin through hole (PTH) components that is more typical for smaller series or simpler designs. The technique is based on one or more hot solder waves used to mount components to the PCB. It is suitable for both through hole components and SMD components glued to the board\*.

\* note: it can be SMD component specific, sometimes not recommended due to a quick ramp up to liquidus temperature.

In general, the wave soldering is inducing lower thermal stress to the components compare to the IR reflow profile in respect to the total heat exposure time due to the relatively short peak time. The heat may not penetrate in the short time frame such deeply inside the components as in the case of IR reflow. Nevertheless, wave soldering still present some **higher load in TCE mismatch and peak temperature gradient** with subsequent component damage. A suitable controlled pre-heating is thus recommended to supress the thermal shock impact. (that may be of good help but won't eliminate the TCE load issue)

| Profile Feature                                                           |                    | Pb-Free Assembly | Sn-Pb Assembly   |                            |

|---------------------------------------------------------------------------|--------------------|------------------|------------------|----------------------------|

| Preheat Temperature Min                                                   | T <sub>smin</sub>  | 100 °C           | 100 °C           |                            |

| Preheat Temperature Typical                                               | T                  | 120 °C           | 120 °C           |                            |

| Preheat Temperature Max                                                   | T <sub>s max</sub> | 130 °C           | 130 °C           |                            |

| Preheat Time t <sub>s</sub> from T <sub>s min</sub> to T <sub>s max</sub> | t                  | 70 seconds       | 70 seconds       |                            |

| Peak temperature                                                          | T                  | 245 °C - 260 °C  | 235 °C - 260 °C  |                            |

| Time of actual peak temperature                                           | l t                | 5-8 seconds max. | 3-6 seconds max. |                            |

| Ramp-down Rate, Min                                                       |                    | ~ 2 K/ second    | ~ 2 K/ second    |                            |

| Ramp-down Rate, Typical                                                   |                    | ~ 3.5 K/ second  | ~ 3.5 K/ second  |                            |

| Ramp-down Rate, Max                                                       | 1                  | ~ 5 K/ second    | ~ 5 K/ second    | *****                      |

| Time 25°C to 25°C                                                         |                    | 4 minutes        | 4 minutes        | ECONTRACTOR AND A CONTRACT |

| Applied cycles                                                            | 1                  | 1 cycle max.     |                  |                            |

Fig.4. wave soldering (two waves) typical layout, lead-free wave soldering profile and characterisation – refer to EN61760-1:2006

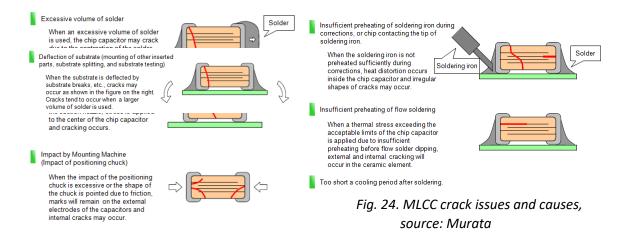

**Insufficient pre-heating** before the flow soldering or solder dipping may be critical due to the TCE mismatch considerations to sensitive components such as MLCC capacitors. When the thermal stress is exceeding the acceptable construction limit, some external and internal cracking may occur in the ceramic element body.

#### 4.1.3. Vapour Phase Soldering

Vapour phase soldering has been suited more towards lower volume PCB assembly production, mainly due to the cost and extended cycle times, nevertheless step by step it is used more often even at medium volume productions now. Vapour phase well suits high mix, low volume boards and eliminates the need for unique reflow profiles to be created for each product, which can take time. The vapour phase profile, on the other hand, needs to be set up reflecting size of the board and thermal inertia (see the next paragraph).

Vapour phase technique is using boiling of an inert heat transfer liquid (e.g. perfluoropolyether PFPE) condensing on the PCBs. The liquid used is chosen with a desired boiling point in mind to suit the solder alloy to be reflowed. Unlike convection reflows, where the PCB travels through heating zones on a conveyor belt, vapour phase ovens are smaller in footprint and the PCB remains fixed in place. The physical height of the PCB is then adjusted so that it sits within, as well as above or just on the surface of, the vapour layer which completes the reflow process. Ref [3]

During the process very little temperature difference (compare to IR reflow) occurs between components of different thermal mass (for example: a large metal heat sink, compared to 0603 chip

resistors), which makes it very good for densely populated PCBs and reduces the need for convection reflow peak temperature margin over the solder paste melting point. Thus vapour phase reflow can provide reliable solder joints at lower peak temperature compare to the IR convection reflow.

Fig.5. typical vapour phase mounting temperature profile

Components thermal load during vapour phase is usually lower compare to the IR convection reflow due to the lower peak temperature, nevertheless attention has to paid to the **peak temperature gradient** and **time above a certain high temperature** not to exceed the component specification. Preheating shall be also applied with vapour phase soldering to reduce thermal issues and improve solder joint quality.

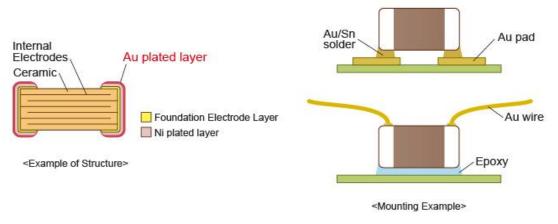

#### 4.1.4. Wire Bonding

Component wire bonding connection is used in some special, lower volume applications such as high temperature or RF applications. **Gold plated component termination finish is required** in this case. The component is fixed to the board by epoxy glue and connected by ultrasonic gold wire bonding to the components' top surface.

Au-Sn (80/20) brazing alloy at 300 to 320 °C in N2 atmosphere is typically recommended for die bonding conditions of components. Substrate temperature has to match the temperature of the brazing alloy, then the brazing alloy can be placed on the substrate and the component on the alloy. The part shall be hold in position with gently applied load. The operation time shall not exceed 1 minute.

Gold wire 25 micro m (0.001 inch) diameter can be recommended for wire bonding method. The wire bonding joint is performed by thermo-compression and ultrasonic ball bonding. Required stage temperature is within 150 to 200  $^{\circ}$ C with wedge or capillary weight: 0.2N to 0.5N

The wire bonding method is usually providing a high reliability mount solution with **robustness** against corrosion/oxidisation and environmental load. Nevertheless, vibration resistance, noise and ESL issues have to be carefully examined.

Fig.6. MLCC gold plated capacitor structure and wire bonding methods, source: Murata

#### 4.1.5. Adhesive Bonding

The other alternative component board mounting method is an adhesive bonding. The conductive glue that consists of conductive particles in organic adhesive/binder provide the

mechanical and electrical joint between the component and PCB pads. The adhesives can be of "hard" type such as epoxy or "soft" type such as silicon based materials. The adhesives are loaded with usually silver or graphite conductive particles to form isotropic or anisotropic mount glue.

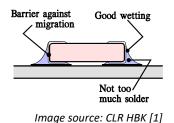

Image source: CLR HBK [1]

Low thermal stress and environmental friendly process are the key advantages of adhesive bonding technology. Overall cost, reliability, mechanical strength and electrical conductivity stability under humid conductions are the main concerns associated with this method.

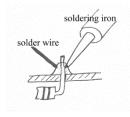

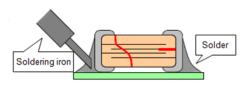

#### 4.1.6. Hand Soldering

Hand soldering is mostly used for small scale production or re-work operations. In general, hand soldering is not recommended by number of component manufacturers due to the reproducibility and high process variability issues. Requirements of "perfect" solder joint visual standard can sometimes end-up with a nice, shiny solder joint finish, however uncontrolled thermal overstress to the components by not-properly trained operators.

As with wave soldering, the insufficient pre-heating before the soldering may cause some **TCE mismatch issues** to components such as MLCC capacitors. Insufficient preheating of soldering iron during corrections, or chip contacting the tip of soldering iron may cause heat distortion inside the chip capacitor and cracks may occur in the structure.

Image source: Murata

See Fig.7. for general hand soldering recommendations, nevertheless check and follow the manufacturer recommendations for a specific component type.

| Tip Diameter           | Slected to fit application |

|------------------------|----------------------------|

| Max.Tip Temperature    | 350 - 370°C *              |

| Anti-Static Protection | Required / Non-required    |

| Max. Exposure Time     | 3s                         |

\* manufacturer and series specific (check recommendations)

#### Fig. 7. General recommendation for hand soldering parameters

Hand soldering at high temperatures can also cause contamination. This contamination & high temperature may cause deterioration of the component overcoat, which could lead to field failures.

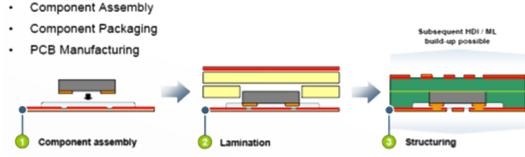

#### 4.1.7. PCB Embedding

Passive components are representing as much as 70% of PCB footprint. The development of a suitable technology whereby integrated passive components is embedded into the PCB body has been one of the key trends in downsizing for more than a decade. The 'embedding technology' have been already implemented from pre-production to mass production in number of applications.

Embedding electronic components has been described in publications either as a technique which creates the components directly during PCB manufacturing or as a process where currently existing, specially designed or common electronic components inserted into the inner layers of a board.

#### Components are embedded inside an organic substrate / PCB core by combination of

*Figure 8. shows general description of the embedding technology in three steps; source: AVX*

- 1. Component assembly individual components are placed onto pre-prepared copper foil in a specific position according to the design.

- 2. Component packaging Step by step treated foils of substrate are placed around and on top of the devices followed by another copper foil. Under pressure and temperature, the sandwich is laminated together to create the core of the new PCB.

- 3. PCB manufacturing The third step is structuring the copper tracks and layers into required circuits and the construction of the PCB achieved using existing procedures.

As well as the main advantage, which was already mentioned, namely, the efficient usage of the inner space of the PCBs which leads to a reduction in overall size or an ability to include additional features in the same foot print, passive embedding technology offers other benefits such as improving certain physical and electrical properties.

- Improvement of electrical parameters (for example shorter distance between components)

- Increased reliability (components encapsulated in a protective environment)

- Better resistance to mechanical stress

- Improved thermal properties (better heat sinking)

- Design copy protection.

- Lower thermal shock stress during mounting compare to IR reflow

However, challenges include:

- 3D design skills required

- Supply chain of both, embedding technologies and passives is still limited

- No repair, No rework possible

#### **Component requirements:**

Apart from the normal parameters driven by the functionality of passive components, for embedded technology applications, thickness is the most important overall dimension. PCB manufacturers have the ability to embed different thickness of devices depending to number of PCB layers. The standard single PCB layer is typically requiring **maximum component thickness 150µm**. The component challenges are not only in the maximum component thickness itself, but also it covers **tight control of termination thickness variability**. **Thus use of a specific embedded process ready components is necessary.** Surface finishing may also need some modification to fit better into the construction technology used for the inner structure of the PCB. Standard component technology typically uses a Ni/Sn layer to guarantee a suitable solderability performance for SMD technology. However, for embedding technology processing a **copper layer termination surface finish** is a better option (depending on assembly technology). There are currently some MLCC embedded capacitors available on the market in maximum thickness of 0.15mm and some specific designs of tantalum capacitor with thickness 0.5/0.6mm suitable for the embedding processing. Source: AVX [6]

#### 4.2. Common Soldering Process Issues

#### 4.2.1. Oxidisation

Fast oxidisation is a common issue related to high temperatures and presence of oxygen during the convection reflow or wave soldering processes. The oxidisation may induce some degradation of metal surface and its environmental robustness, thus impacting the components and the electronic hardware lifetime.

The level of oxidisation is depending on more factors, the second most important (after the degree of temperature itself) is a selection of activation flux that is part of the solder paste. More "aggressive" flux is improving the solder wetting and solder joint strength, on the other hand it is increasing oxidisation and require thorough cleaning process to remove all flux residual. **Despite, common practise, most component manufacturers do not recommend use of highly activated fluxes due to this reason**.

**Soldering in an inert gas atmosphere**, typically nitrogen, can be recommended to avoid use of highly activated fluxes and as a way to suppress amount of oxygen present during the soldering process. The use of nitrogen also significantly increases the wetting force and thus it improves solder joint quality. Of course, the main down side is increase of the mounting process cost.

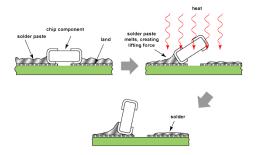

#### 4.2.2. Component displacement

Some component displacement may occur during board mounting, especially during mass production using convection IR reflow oven. The component displacement is caused by changes of surface tension during the thermal flow. The component moves to a position

with "minimal energy" that can be observed as:

**Component self-alignment** – in case of correct PCB pad design and uniform thermal profile, the component is self-centred on the position – this is ideal, target stage of the right mounting process and PCB layout design set up.

**Skewed "swimming" components or tombstoning** ('Manhattan effect', 'drawbridging', or 'Stonehenge effect')

During the component "swimming" displacement, the mounted parts are skewed outside of their PCB pads centre position. "Tombstoning" effect happens, when one component side is lifted upwards (see drawing). These faulty component placement phenomena are caused by uneven wetting forces between the component sides during soldering. There are number of factors that are influencing these issues, such as:

- different heat capacity connected to the pads

- pad design layout and position

- solder paste printing mis-alignment

- Wettability differences between the two terminations

- faulty solder paste application

- faulty pick and place process pushing one termination stronger inside the solder paste

- misaligned component placement

Tombstoning occurs more frequent with short, wide terminations, and with thin & light devices such as miniature capacitors and resistors. The wetting forces vary with chip dimensions; the downward forces vary with the square of the chip dimensions.

#### 4.2.3. Outgassing

Non-hermetic, epoxy based packages used by number of component designs are featuring a micro porous structure that may act as a moisture residuals traps. While, the components itself are designed and constructed to operate reliably in accordance to their specifications, some outgassing and fast moisture evaporation can occur during the high temperature board mounting process.

Outgassing itself may not present a danger for the components itself, if the reflow conditions such as preheat and temperature gradients are within the manufacturer specifications. However, the issue arises for high density mounted PCBs, where small & light components are placed very close to large components. **Outgassing from large components can blow out and displace nearby small parts** in this case. As an example 7343 SMD chip tantalum capacitors can blow out small 0201 MLCC capacitors placed very closed to the capacitor body.

The prevention and recommendation especially for highly populated PCBs would be to **use dry packed components or use appropriate pre-dry process to remove maximum moisture out of the components packaging**.

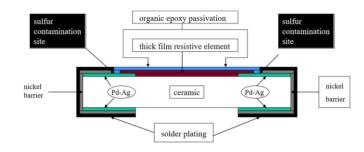

#### 4.2.4. Sulphur Contamination

Sulphur contamination is mainly associated with use and reliability of thick-film chip resistor with Ag-system as inner termination. The silver in the inner termination is very susceptible to contamination via sulphur which produces silver sulphide in chip resistors. Silver is so susceptible to combination with sulphur that the sulphur diffuses through the outer termination layers to the inner termination forming silver sulphide. Silver sulphide unfortunately makes the termination material non-conductive and effectively raises the resistance value until it is essentially **open circuit**. The reaction velocity in this case is influenced by sulphur gas density, temperature and humidity greatly. **This process can be initiated or inhibited already by heat-stress while mounting.**

*Figure 9. Sulphur contamination of thick film resistors; source: Stackpole Electronics, Inc.*

Sulphur can be found in various types of oils and lubricants, rubber gaskets, hoses, belts, and grommets, connectors, and in some applications in the very air that the electronic device operates in. Silver sulphide contamination is a latent failure mode that is undetectable at the time the resistor is manufactured and when the resistor is mounted into its electrical circuit.

Factors such as incomplete or misaligned passivation, incomplete plating, and using low palladium materials for the inner termination, can accelerate the formation of silver sulphide on the chip and lead to failure much faster than would be expected. There are remedies for each of these issues, but all involve increased manufacturing cost which is never popular when considering thick film commodity chip resistors. [16]

Inert gas atmosphere mounting (as mentioned in this chapter above) can be recommended as a prevention measure to suppress the sulphide contamination issues.

#### 4.3. General Measures to Enhance Components' Soldering and Mounting Capabilities

- TCE mismatch ready, proper material selection

- termination solder finish type

- anti-migration barriers

- moisture barriers (impregnation)

- dry packaging

- post-reflow treatment ageing recommendation

**TCE mismatch** presents one of the key component construction challenges to manufacturers. Selection and development of right materials are key for balance between robustness, specification

and cost, thus it can be one of the main differentiator between products for different applications, temperature range and reliability levels.

The **termination solder finish** is depending on mounting process (see the previous chapter) and solder type (SnPb/leadfree ....). **Anti-migration** termination sub-layers are used to supress diffusion and oxidisation processes that may degrade terminations solderability during storage. The selection of the anti-migration layers depends on lead types and components. Nickel layer is commonly used as an excellent diffusion barrier, however it is brittle in thick layers, thus with flat terminations such as MLCC chip capacitor, it is used with 1-2 $\mu$ m thickness, while on "bended J-lead" tantalum terminations nickel thickness is just 0.1-0.2  $\mu$ m, as thicker nickel would crack in bend area resulting in diffusion, growth of intermetallic alloys and loss of solderability.

Moisture, together with temperature and voltage is one of the main accelerating factors for diffusion and oxidisation degrading process. Thus many components are today using some form of **moisture barriers** such as silicon/oil impregnation or **dry packing**. Dry packing can be recommended as a preventive measure to suppress mounting thermal issues on all components. Where dry packing cannot be used or it is not practical, some components pre-dry process prior mounting would be recommended in order to suppress the component history/storage/manufacturing moisture related variation.

### 5. Component Manufacturers Mounting Guide Survey

#### 5.1. Board Design and Component Pre-Assembly Preparation

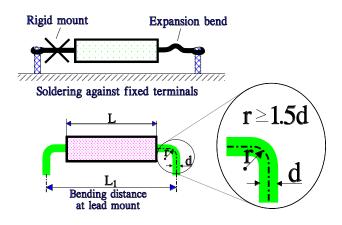

The leads of **leaded components** shall be bent and often cut to the right length before they are mounted / soldered to the substrate. *Lead cutting, bending and mounting are operations that may be hazardous* if they are not performed properly.

Fig.10. leaded components basic mounting rules, source: CLR HBK [1]

Components mounted to soldering terminals must be provided with a small expansion bend on the leads (Figure 10). Otherwise we shall run the risk that temperature dependent contractive forces will be transferred to internal contact areas causing them to fracture and create an open circuit. This kind of an open circuit usually appears intermittently and is, of course, temperature dependent; that will make the trouble shooting difficult and uncertain.

When the connecting leads are bent it has to be done according to specific rules. If we bend too close to the component body, we run a great risk of transferring forces to internal connections that could be damaged. The forces may also cause cracks in hermetic seals. With Figure 8. as a starting point we can write the following equation:

, where **n** is the lowest possible integer fulfilling Equation 1. M stands for used modulus of the board layout, 2.5 or 2.54 mm. For small component bodies sometimes half the modulus needs to be used in order not to make the bending distances unnecessarily large. With large bodies standardizing may justify that *n* is limited only to odd values. Capacitors and magnetic devices (no heat produced) *heavier than 5 - 10 gram* should be fixed mechanically attached to the substrate.

If **power leaded components** are soldered to turrets as shown in the top example of Figure 10. we have to ensure that the **heat transfer** through the leads doesn't melt the solder. In critical cases it may be necessary to choose longer or thinner leads, less heat conductive lead material or, alternatively, we must decrease the power developed in the component or bond it to the PCB with a thermal adhesive.

We must also see to it that the height over the substrate is adequate with respect to allowing sufficient **thermal radiation**. Heat from the soldering process may, in unfortunate cases, be conducted up through the leads melting the internal solder connections in radial lead components that are mounted close to the circuit board. To avoid this, we should ensure that those connections are made with a high-temperature solder.

**Cutting a component lead** with side cutting pliers will expose the component to a considerable mechanical shock. This applies also to automatic lead cutters. The shock is of short duration and the magnitude may vary strongly from one type and manufacture to another. If such components are used whose construction may be sensitive to mechanical shocks, the mechanical forces should be measured and the exposure to the cutting forces evaluated. A cutting plier with a flat edge toward the component reduce this shock.

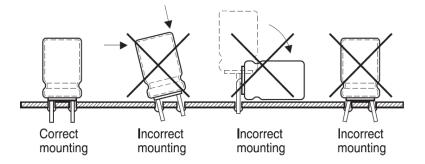

#### Mounting considerations for single-ended components

The internal structure of single-ended components might be damaged if excessive force is applied to the lead wires. Stresses like push, pull, bend etc. might cause electrical parameters deterioration or open/short circuit, due to rupture of terminals or internal elements.

Pay attention to the following cautions:

- Do not move the component after soldering to PC board.

- Do not pick up the PC board by holding the soldered component.

- Do not insert component on the PC board with a hole space different to specified lead space.

- Check the recommended component position into consideration when designing the PC board layout.

Fig.11. mounting considerations for single-ended capacitors, source: TDK

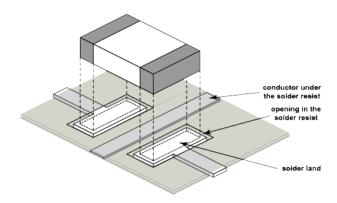

#### SMD component pads

should be designed to achieve good solder filets and minimize component movement during reflow soldering. Pad designs – see manufacturer's datasheets for pad design recommendations. The basis +of these designs may include:

- Pad width equal to component width. It is permissible to decrease this to as low as 85% of component width but it is not advisable to go below this.

- Pad overlap 0.5mm beneath component.

- Pad extension 0.5mm beyond components for reflow and 1.0mm for wave soldering.

Some common pad design related mounting problems and recommendations are shown in Fig.12. Below.

| ltem                          | Poor example           | Recommended example/Separated by solder resist |  |

|-------------------------------|------------------------|------------------------------------------------|--|

| Multiple parts mount          |                        | Solder resist                                  |  |

| Mount with<br>leaded parts    | Laded parts            | Solder resist<br>Leaded parts                  |  |

| Wire soldering after mounting | Soldering iron<br>Wire | Solder resist                                  |  |

| Over View                     | Solder resist          | Solder resist                                  |  |

Fig 12. Typical SMD mounting problems and recommended solution. Source: Kyocera

The correct layout of **solder resist**, as used in Figure 12. examples, can mitigate certain mounting issues. See Fig.13. solder resist layout design example on SMD component.

Figure 13. solder resist on a printed wiring board, source: Epectec [4]

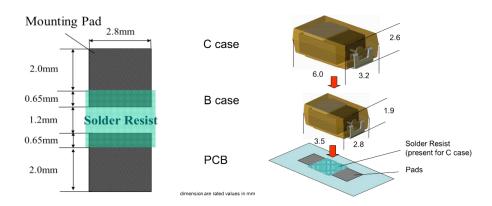

Solder resist can be used also in some cases to modify pad design in relative inexpensive way to adjust to new component or fix a pad layout issue. A flexible pad design concept using solder resist masking that allows flexible replacement of C and B case tantalum capacitors was suggested by AVX – see Fig.14. Smaller B case size can offer cost saving over larger C case size when it is available / qualified without need of expensive circuit board pad re-design.

Figure 14. tantalum capacitors C to B case universal pad design, source: AVX

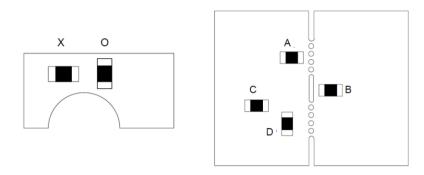

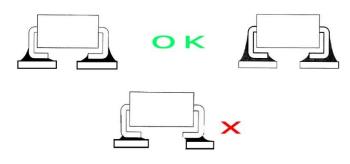

It is important to remember that SMD components, more than the others, are influenced by temperature changes, especially for the larger component. Thus, **dimensions and mounting directions are most important.** Further, short and wide bodies are preferable to long and thin ones, partly for strength reasons, partly because of the inductance and with that the frequency dependence will decrease. Still another reason is that constraint density in solder joint from coefficient of expansion between substrate and chip decreases in significance with shorter distances between terminations. This approach results in a strongly improved mechanical strength, better electrical parameters and thermal dissipation. This would be a typical recommendation for assembly of mechanically sensitive MLCC capacitors – see Fig.15. The same principle works on MLCC "reverse geometry" types, where the terminations are made alongside the longer dimension of the chip.

Recommended chip position on PCB to minimize stress from PCB warpage

Fig.15. recommended MLCC chip PCB position, source: Kyocera

Since the stress to the curvature or bending at the time of breaking printed substrate, may cause fault when arranging surface mount components near printed substrate breaking point, consideration is required for the method of arrangement of surface mount components. (see also chapter 4.2.8.).

*Fig. 16. SMD component arrangement close to curvature, bending or PCB crop lines. Source: Panasonic*

The above figure 16. Illustrates mechanical stress considerations related to the SMD component PCB layout orientation. Risk of mechanical issues on the Fig 16. right side can be assumed:

#### A > C > B >>>>>> D

Therefore, arrange to the break line of printed substrate as in parallel as possible, keep away from break line as much as possible or use milling machine/tool to perform the cut.

Passive components chips may produce also some heat and, to some extent, also SM magnetics. In comparison with lead mount components the heat conduction through the solder joints of the SMDs is good. Hence the relative temperature of the body centre with respect to non-SMDs will decrease and will rise in the solder joints. A wide lead pattern will facilitate the heat transfer still more.

It will allow a larger electric load before we reach the specified "hot spot" temperature. Nevertheless, the **thermal dissipation and radiation has to be considered during the PCB and pad layout design**.

Because of their size SMD styles always must be furnished with flexible leads in order to prevent damage during temperature cycles. Heavier components, in order to prevent them from coming loose when subjected to shock or vibration, should be mechanically attached to their substrate by means of an adhesive or staking compound.

#### 5.2. Component Spacing

For wave soldering, components, must be spaced sufficiently far apart to avoid bridging or shadowing (inability of solder to penetrate properly into small spaces). This is less important for reflow soldering but sufficient space must be allowed to enable rework should it be required. At least <u>0.5 mm</u> <u>air space</u> or additional insulation should separate components from adjacent metal parts, for example conductive patterns on printed circuit boards.

#### 5.3. Component Handling

**Commercial non-hermetic components** should be handled with care to avoid damage or contamination from perspiration and skin oils. The use of tweezers or vacuum pick-ups is strongly recommended for individual components. Bulk handling should ensure that abrasion and mechanical shock are minimized. Taped and reeled components provides the ideal medium for direct presentation to the placement machine. Any mechanical shock should be minimized during handling of components, especially chip multilayer ceramic capacitors.

**Multiple leads components** (such as some SMD film capacitors, arrays etc.) terminations flatness shall be maintained and it may not be modified during the different component mounting steps (cleaning, assembling, ...). Solder wetting may not be sufficient on all terminations equally if for example one lead is not bent far enough and it doesn't touch the PADs completely on its surface.

**Leaded components** should not be handled by terminals or by connections. It is advisable to short-circuit the connections of high voltage capacitors (over 120V in normal environment) after their use under D.C. voltage, as certain dielectrics keep a residual charge which might be dangerous during handling operations.

The **fluid impregnated capacitors**, unless otherwise specified, shall be mounted with the terminals faced upwards. A free gap shall be allowed between battery-mounted capacitors. Cables, bars or connecting braids shall be properly dimensioned to prevent any abnormal temperature rise of the terminals. It is also preferable to connect battery-mounted capacitors by means of flexible cables or by braids.

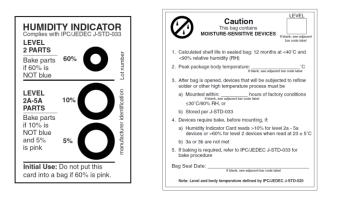

Thin-film and some small passive components can exhibit some sensitivity level to **Electrostatic Discharge (ESD)**, ESD charge/discharge voltage can exceed tenth of kilo-Volts and the ESD typical charge current can be around 1 to 10A in many cases. Please refer to the manufacturing datasheets about ESD sensitivity of the specific component. ESD sensitive components shall be handled with an ESD conform tweezers and if handled manually, please wear anti-static wrist strap and finger gloves to avoid ESD stress and dust. ESD may not be considered as a critical factor for high capacitance, high charge storage capacitors such as electrolytic capacitors on the other hand. The amount of ESD charge can be easily absorbed by high capacitance devices without a substantial increase of the applied voltage. For ESD classification and further info please refer to IPC/JEDEC-EIA-625 standard. Moisture sensitive device are necessary to be handled and processed following its **moisture sensitivity level (MSL)** as per industrial standard J-STD-033C. The MSL rated component has to be dry packed with humidity indicator and caution statement – see Fig. 17.

Fig.17. Example of humidity indicator and caution statement as per the J-STD-033C

The components shall be processed within an indicated floor life time. Drying and baking before mounting in accordance to the caution instructions are required in case of longer exposure after the bag is opened. MSL classification and floor life time – see fig.18.

| Moisture<br>Sensitivity<br>Level | Floor Life (out of bag) at factory<br>ambient ≤30 °C/60% RH or as stated                                    |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| 1                                | Unlimited at ≤30 °C/85% RH                                                                                  |  |  |

| 2                                | 1 year                                                                                                      |  |  |

| 2a                               | 4 weeks                                                                                                     |  |  |

| 3                                | 168 hours                                                                                                   |  |  |

| 4                                | 72 hours                                                                                                    |  |  |

| 5                                | 48 hours                                                                                                    |  |  |

| 5a                               | 24 hours                                                                                                    |  |  |

| 6                                | Mandatory bake before use. After bake,<br>must be reflowed within the time limit<br>specified on the label. |  |  |

Fig.18. Moisture classification and floor life – refer to J-STD-033C

#### 5.4. Pick & Place

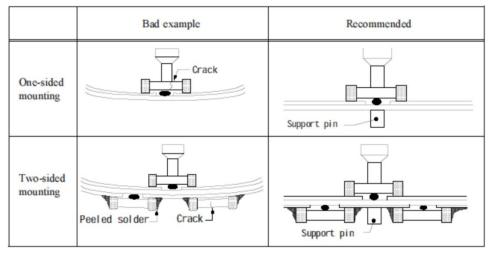

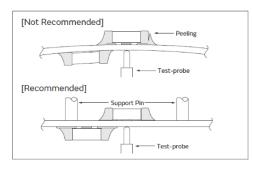

Fast **pick and place** on large boards may also induce some cracks in chip components such as MLCC capacitors during the component placement. Pressure applied by the Pick and Place nozzle during placement should be carefully monitored and limited. Use of supporting pins to the other PCBs side may limit the board bending and thus reduce mechanical stress to MLCCs. See the following Fig 19.

Fig 19. large board flex suppression by support pins, source: Kyocera

Similar situation as in Fig. 19. can happen during electrical testing of PCBs when test probes are contacting the PCB with push force – see Fig.20. It is recommended to confirm position of the

support pin or specific jig, when inspecting the electrical performance of a component after mounting on the printed circuit board. The thrusting force of the test probe can flex the PCB, resulting in cracked chips or open solder joints. The use of support pins on the back side of the PCB can prevent warping or flexing. The support pins shall be positioned as close to the test-probe as possible. Avoid vibration of the board by shock when a test-probe contacts a printed circuit board.

#### Fig 20. large board flex during testing, source: Murata

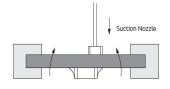

#### Pick and Place of nearby Components (source: Murata)

Pick and place of nearby and opposite side components can also cause some flex and PCB vibration. Board deflection stress may damage the back side (bottom side) components if the bottom dead point of the suction nozzle is set too low. After the board is

straightened, it is important to set the bottom dead point of the nozzle on the upper surface of the board. Periodical check and adjustment of the bottom dead point is advised as a preventive measure.

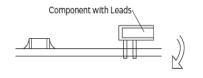

When inserting larger leaded components (transformers, etc.) into boards, the board bending may cause cracks in chip components or cracks in solder joints. The insertion stress can be reduced by appropriate hole size enlargement. It is recommended to fix the board with support pins or a dedicated jig before insertion.

Periodically check that there is no difference in the height of each support pin during mass production.

Insertion and removal of sockets and connectors, etc., might be additional cause of board bending. The board shall not warp during insertion and removal of sockets and connectors, etc.

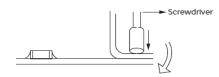

The board may be bent, when tightening screws during attachment of the board to a shield or chassis etc. Mechanical assembly process shall be prepared to minimize board bending, flexing or vibration. Use of torque screwdriver is recommended to prevent over-tightening of the screws. Please note that the

board straightness may be impacted by thermal reflow soldering stress. The stress may be applied to the chips by forcibly flattening the board when tightening the screws.

#### 5.5. Soldering

What is the optimum soldering conditions and solder fillet? The best solder fillet for all SMT applications is one which makes a reliable connection and which best withstands the environmental exposures of the products with minimum degradation. This fillet is difficult to describe quantitatively for all parts. The optimum fillet ranges in height from about 1/3 to 2/3 of the part termination height. This does not mean that all solder joints outside of this range should be repaired. It does mean that this is the target for the process engineer to reach for in his process. As many as possible of the solder fillets on the board should be in this range. [5]

The minimum amount of solder to give a good joint should be used. Excessive solder can lead to damage from the stresses caused by the difference in coefficients of expansion between solder, chip and substrate. If hand soldering cannot be avoided, the preferred technique is the utilization of hot air soldering tools.

In general, most of capacitors and resistors are suitable for all vapour phase wave and reflow soldering systems, nevertheless please check the manufacturer's relevant datasheets and guidelines. Common temperature profiles and specifications - see the industry standards Chapter 2.

**Some limitation exists mainly for film capacitors** regarding the use of convection profile and maximum peak temperature. Temperature profiles are specified in the CECC 00802 standard. Temperature peak limits for most common film dielectrics are:

- P.E.T. = 215°C (20 s at 40 s)

- P.E.N. = 230 C (20 s at 40 s).

**Important note: PET film capacitors are not designed to withstand a lead-free reflow cycle,** use of vapour phase mounting can be recommended. See Fig.21 below for PET SMT film capacitors vapour phase profile recommendation.

#### Profil thermique de report phase vapeur recommandé / Vapor phase reflow profile recommendations

Fig.21. PET SMT film capacitors vapour phase profile recommendation, source: EXXELIA (in accordance to CECC00802)

#### 5.5.1. Flux

Use of **mildly activated rosin fluxes** in the solder are preferred. More "aggressive" flux is improving the solder wetting and solder joint strength, on the other hand it is increasing oxidisation and require thorough cleaning process to remove all flux residual. **Most manufacturers do not recommend use of highly activated fluxes due to this reason**. Water soluble fluxes are not recommended for some resistor technologies using a thin resistive film. Water soluble fluxes are very aggressive in stripping off oxides and if you do not completely clean the residue off, then it can continue to eat away at the base metal. Please follow the manufacturers specification for details.

#### 5.5.2. Preheat

It is important to avoid the possibility of thermal shock during soldering and carefully controlled preheat is therefore required. The rate of preheat should not exceed 4°C/second and a target figure 2°C/second is recommended. Although an 80°C to 120°C temperature differential between preheating and peak temperature is preferred, recent developments allow a temperature differential between the component surface and the soldering temperature of 150°C (Maximum) for capacitors of 1210 size and below with a maximum thickness of 1.25mm. The user is cautioned that the risk of thermal shock increases as chip size or temperature differential increases.

#### 5.5.3. Cooling

Natural cooling in air is preferred, as this minimizes stresses within the soldered joint. When forced air cooling is used, cooling rate should not exceed 4°C/second. Quenching is not recommended but if used, maximum temperature differentials should be observed according to the preheat conditions above.

#### 5.5.4. Solder Joint Quality

Soldering quality shall be regularly examined in order to access the mounting process correct set-up. The solder joint has to provide sufficient mechanical strength and electrical features. One of the critical factor for SMD "J" type is a full coverage of the termination bend area with a sufficient solder wetting that ensures proper solder joint mechanical strength.

Reflow conditions (tinning thickness on boards, amount of soldering paste

deposited, reflow soldering process, etc.) should allow, after reflow, a solder filet on the SMD "J" lead components look as shown on Fig.22. Solder height should cover the connection bend by about 0.5 mm and finish on the vertical side of the connection. Good wetting ability of the solder fillet can be assess with the wetting angle.

Fig.22. acceptable (top) and not acceptable (bottom) solder joint per EN NF 61192-2 AFNOR

#### 5.6. Cleaning

Flux residues may be hygroscopic or acidic and must be removed. Passive components are usually acceptable for use with all of the solvents described in the specifications MIL-STD-202 and EIA-RS-198. Alcohol based solvents are acceptable and properly controlled water cleaning systems are also acceptable.

Care should be taken to ensure that the components are thoroughly cleaned of flux residues especially the space beneath the component. Such residues may otherwise become conductive and effectively offer a low resistance bypass to the capacitor.

Excessive ultrasonic power or direct vibration transfer to a printed wiring board may generate a resonant vibration in the board. This may cause a crack in sensitive components (such as MLCC capacitor) or its solder joints to the board and degradation in the terminal strength of the capacitor. In order to avoid this, the following cleaning conditions are recommended:

| Power:     | ≦20 W/L |

|------------|---------|

| Frequency: | ≦40 kHz |

| Duration:  | ≦5 min  |

#### NOTE: The details is referred to JEITA ET-7405, and the bath size is 250 mm X 200 mm X 180mm(depth)

The most commonly recommended ultrasonic frequency is 40 kHz. It is considered the "universal frequency" because it is generally safe for use in most applications and will produce the most intense cavitation energies to remove the most common types of contaminants (oil, grease, metal chips) from the widest range of substrates. Lower frequencies such as 20 or 25 kHz produce larger cavitation

bubbles which are more aggressive when they implode. Higher frequencies (68-250 kHz) will produce smaller cavitation bubbles with less intense energies, but more of them. [19]

Before starting your production process, test your cleaning equipment/process to insure it does not degrade the components. Exposure to harsh ultrasonic cleaning after mounting; shower washing; covering with masking tapes may cause component termination(s) to peel. Caution should be taken when cleaning is performed.

#### 5.7. Post Solder Handling

Once SMD components are soldered to the board, any bending or flexure of the PCB applies stresses to the soldered joints of the components. For leaded devices, the stresses are absorbed by the compliancy of the metal leads and generally don't result in problems unless the stress is large enough to overcome the stress relief provided by the lead.

Ceramic capacitors are more susceptible to such stress because they don't have compliant leads and are brittle in nature. The most frequent failure mode is low DC resistance or short circuit. The second failure mode is significant loss of capacitance due to severing of contact between sets of the internal electrodes. [8]

#### Common Causes of Mechanical Cracking

Cracks caused by mechanical flexure are very easily identified and generally take one of the following two general forms:

*Fig.23.* Angled crack between bottom of device to top of solder joint and fracture from top of device to bottom of device. source: AVX

Mechanical cracks are often hidden underneath the termination and are difficult to see externally. However, if one end termination falls off during the removal process from PCB, this is one indication that the cause of failure was excessive mechanical stress due to board warping.

If a board mounted with capacitors is held with one hand, the board may bend. Firmly hold the edges of the board with both hands when handling. If a board mounted with capacitors is dropped, cracks may occur in the capacitors. Do not use dropped boards, as there is a possibility that the quality of the capacitors may be impaired.

The most common source for mechanical stress is board depenalization equipment, such as manual break apart, cutters and shear presses. Improperly aligned or dull cutters may cause torqueing of the PCB resulting in flex stresses being transmitted to components near the board edge.

Another common source of flexural stress is contact during parametric testing when test points are probed. If the PCB is allowed to flex during the test cycle, nearby ceramic capacitors may be broken.

A third common source is board to board connections at vertical connectors where cables or other PCBs are connected to the PCB. If the board is not supported during the plug/unplug cycle, it may flex and cause damage to nearby components. Special care should also be taken when handling large (>6" on a side) PCBs since they more easily flex or warp than smaller boards.

#### 5.8. PCB Coating, Potting and Molding

In general, coating, potting, molding or sealing of the assembled PCB can be recommended in order to supress moisture, oxidisation and other environmental impacts. Nevertheless, the process has to follow the manufacturer specifications as it can affect the mounted components parametric values (such as capacitance, resistance, ESR, DCL etc.) due to a thermal stress effect, TCE expansion or shrinkage of the component overcoat/moulding package etc.

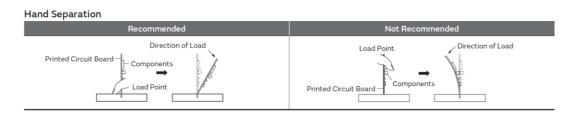

#### 5.9. PCB Cut and Cropping

Check the cropping method suitability for the printed circuit board in advance. Printed circuit board cropping shall be carried out by using a jig or an apparatus (disc separator, router type separator, etc.) to prevent the mechanical stress that can occur to the board. The board separation recommendation from Murata – see Fig 25.

| Denud Committee Mathed   | Hand Separation<br>Nipper Separation                                                  | (1) Board Separation Jig                                                                          | Board Separation Apparatus                                                                                     |                           |  |

|--------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------|--|

| Board Separation Method  |                                                                                       |                                                                                                   | (2) Disc Separator                                                                                             | (3) Router Type Separator |  |

| Level of stress on board | High                                                                                  | Medium                                                                                            | Medium                                                                                                         | Low                       |  |

| Recommended              | ×                                                                                     | ∆*                                                                                                | *                                                                                                              | 0                         |  |

| Notes                    | Hand and nipper<br>separation apply a high<br>level of stress.<br>Use another method. | <ul> <li>Board handling</li> <li>Board bending direction</li> <li>Layout of capacitors</li> </ul> | Board handling     Layout of slits     Design of V groove     Arrangement of blades     Controlling blade life | Board handling            |  |

\* When a board separation jig or disc separator is used, if the following precautions are not observed, a large board deflection stress will occur and the capacitors may crack. Use router type separator if at all possible.

#### Fig. 25. Board separation method recommendation, source: Murata

In case of hand separation of single side board is used, stress on the component mounting position can be minimized by holding the portion close to the jig, and bend in the direction towards the side where the components are mounted. Not recommended example: The risk of cracks may increase due to large stress being applied to the component mounting position, if the portion away from the jig is held and bent in the direction opposite the side, where the components are mounted – see Fig.26.

Fig. 26. Hand separation technique recommendation, source: Murata

In case of double side board, where the above Fig.26 method cannot be used, consider introducing a router type separator. If it is difficult to introduce a router type separator, mount the components parallel to the board separation surface. When mounting components near the board separation point, add slits in the separation position near the component and keep the mounting position of the components away from the board separation point – see Fig.27.

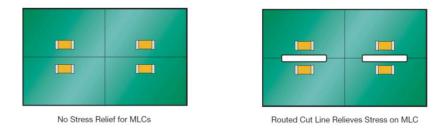

To avoid many of the handling problems, manufacturers are recommending that MLCCs be located at least 5mm away from nearest edge of board. However, when this is not possible, the panel be routed along the cut line, adjacent to where the MLCC is located.

Fig. 27. Routed cut line stress relieve, source: AVX MLCC recommendation

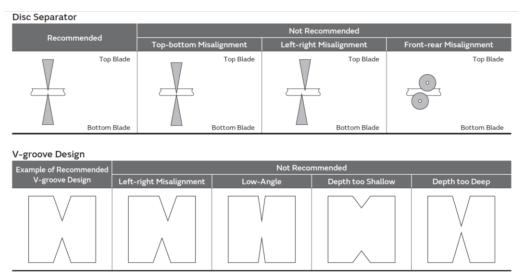

Board deflection stress component cracks may also result in misaligned disc or V groove separation machines set-up. See Fig. 28. IF V groove is too deep, it is possible to brake when you handle and carry it. Carefully design depth of the V groove with consideration about strength of material of the printed circuit board.

Fig. 28. Disc separator and V-groove design recommendation, source: Murata

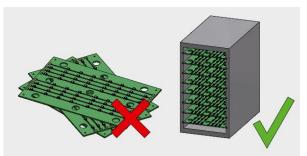

#### 5.10. PCB Storage

By stacking the PCB boards, sensitive components might be deformed or delaminated due to the mechanical stress. Use a proper and suitable rack to keep the finished and assembled PCB boards correctly – see Fig 29.

Fig 29. PCB correct storage, picture source: Würth Elektronik

The PCB has to be stored in "environmental standard" conditions and such conditions has to be also maintained during transportation and manipulation. Extra care has to be paid to sea and air transportation or "unattended on the hold short term storage" at direct sunshine etc.

#### 5.11. Rework

When performing manual repair or reworking, it is necessary to pay attention to the following two issues, particularly because of temperature change and residual stress. It is also necessary to consider thermal capacity of the PCB in order to optimise the rework procedures.

- 1. In order to prevent damage (cracks) to the component caused by localized rapid heating and heat shock: baking of PCB, component preheat or other measures to reduce heat shock to the parts shall be applied.

- 2. The board temperature is lower than that used for reflow soldering, so a difference in residual stress occurs during cooling, and the mechanical strength (resistance to board bending) tends to decrease. In order to increase the strength, it is necessary to maintain a high board temperature during soldering.

#### 5.11.1. Solder Iron Rework

In order to reduce damage to the capacitor, be sure to preheat the capacitor and the mounting board. Preheat to the temperature range depending to MLCC capacitor case size is shown as example in Fig. 30.

| EIA Code      | Temperature of<br>Soldering Iron Tip | Preheating<br>Temperature | Temperature<br>Differential (∆T) | Atmosphere |

|---------------|--------------------------------------|---------------------------|----------------------------------|------------|

| ≤ <b>1206</b> | 350°C max.                           | 150°C min.                | $\Delta T \le 190^{\circ}C$      | Air        |

| ≥ <b>1210</b> | 280°C max.                           | 150°C min.                | $\Delta T \le 130^{\circ}C$      | Air        |

#### Fig. 30. Soldering iron rework recommendation, source: Murata

A hot plate, hot air type preheater, etc. can be used for preheating. After soldering, do not allow the component/PCB to cool down rapidly. Perform the corrections with a soldering iron as quickly as

possible. If the soldering iron is applied too long, there is a possibility of causing solder leaching on the terminal electrodes, which will cause deterioration of the adhesive strength and other problems.

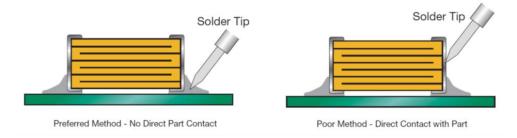

Optimum solder amount when re-working with a soldering iron is needed. If the solder amount is excessive, the risk of cracking is higher during board bending or any other stressful condition. Too little solder amount results in a lack of adhesive strength on the outer electrode termination, which may result in chips breaking loose from the PCB. A soldering iron with a tip of ø3mm or smaller should be used. It is also necessary to keep the soldering iron from touching the components during the re-work. Solder wire with ø0.5mm or smaller is required for soldering. [11]

#### 5.11.2. Spot Heater Rework

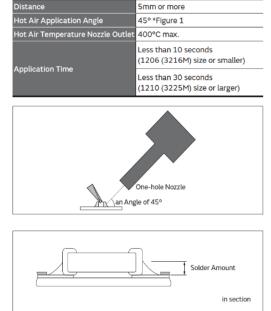

Compared to local heating with a soldering iron, hot air heating by a spot heater heats the overall component and board, therefore, it tends to lessen the thermal shock. In the case of a high density mounted board, a spot heater can also prevent concerns of the soldering iron making direct contact with the component.

If the distance from the hot air outlet of the spot heater to the component is too close, cracks may occur due to thermal shock. To prevent this problem, follow the conditions shown in Fig. 31 on the right.

#### Fig. 31. Hot air rework recommendation, source: Murata

In order to create an appropriate solder fillet shape, it is recommended that hot air be applied at the angle shown in Figure 31.

Thermal shock is common in MLCCs that are manually attached or reworked with a soldering iron. Manufacturers are strongly recommending that any reworking of MLCCs be done with hot air reflow rather than soldering irons. It is practically impossible to cause any thermal shock in ceramic capacitors when using hot air reflow. However direct contact by the soldering iron tip often causes thermal cracks that may fail at a later date. If rework by soldering iron is absolutely necessary, it is recommended that the wattage of the iron be less than 30 watts and the tip temperature be <300°C. Rework should be performed by applying the solder iron tip to the pad and not directly contacting any part of the ceramic capacitor.

Fig. 32. Reworking by hot solder tip, source: AVX mounting guide

#### 5.12. Component Storage