# VII СИНТЕЗ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ

ТЕМА 7.2 РЕГИСТРЫ

Регистры это ПЛС предназначеные для хранения и обработки двоичных слов.

Основные компоненты любого регистра - это триггеры.

Регистры также содержат КЛС для управления триггерами.

Длина регистров определяется количеством триггеров, из которых они состоят.

Регистр с *п* триггерами может хранить n-битное двоичное слово.

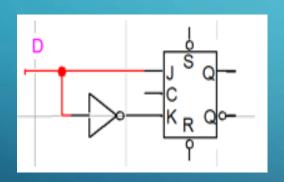

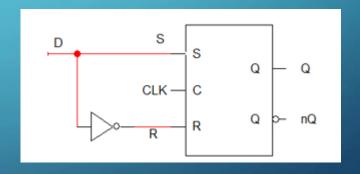

Регистры состоят из триггеров типа D или триггеров JK, RS, которые работают в режиме триггеров D.

В зависимости от выполняемых функций регистры делятся на следующие категории:

- 1. *Параллельные регистры*. Информация должна записываться в эти регистры и считываться параллельно.

- 2. Последовательные регистры или регистры сдвига. В этих регистрах информация вводится и считывается последовательно, бит за битом. Эти регистры могут сдвигать двоичные слова влево или вправо.

- 3. Параллельно-последовательные или последовательно-параллельные регистры, в зависимости от того, как считывается или записывается двоичное слово.

Существуют следующие основные типы регистров:

- **SISO** (Serial Input Serial Output);

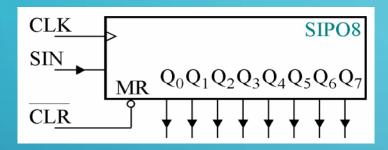

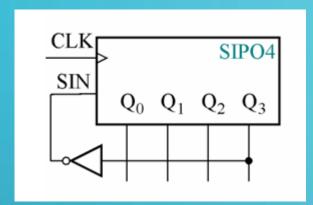

- **SIPO** (Serial Input Parallel Output);

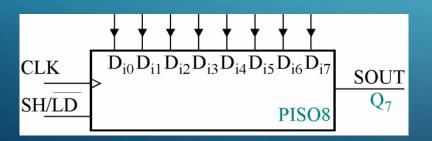

- **PISO** (Parallel Input Serial Output);

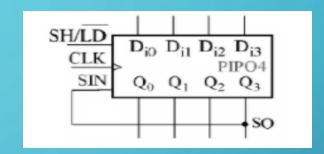

- **PIPO** (Parallel Input Parallel Output).

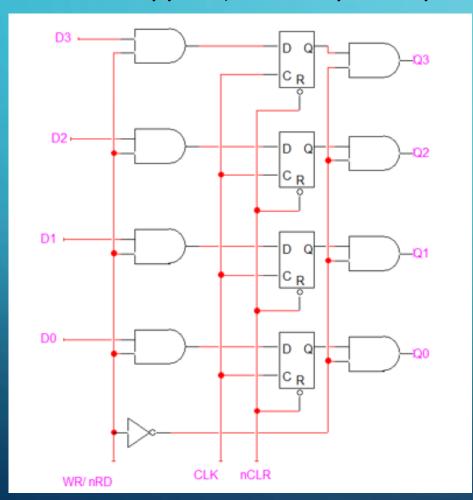

# ПАРАЛЛЕЛЬНЫЕ РЕГИСТРЫ

Основная функция этих регистров - хранить двоичные слова.

Загрузка данных при WR/ nRD=1 (Write/n Read) Паралельное считывание данных приWR/ nRD=0

Вход сброса CLR (clear), активный по логическому нулю служит для асинхронной установки в 0 всех *п* триггеров.

# ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ (СДВИГАЮЩИЕ)

Сдвиг двоичных слов бывает 3-х видов:

- логический

- арифметический

- циклический.

В регистрах сдвига двоичные слова можно^

- вводить последовательно через один из входов, обозначенным  $S_{IN}$  (Serial Input),

- сдвигать двоичное слово вправо или влево

- считывать последовательно только на одном из выходов, обозначенных S<sub>OUT</sub> (Serial Output).

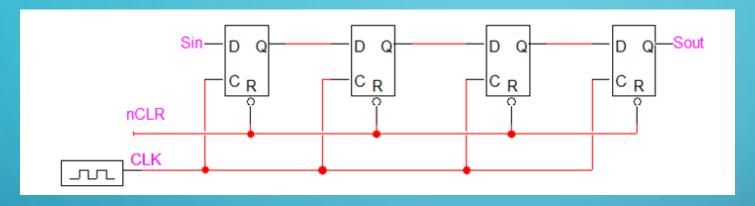

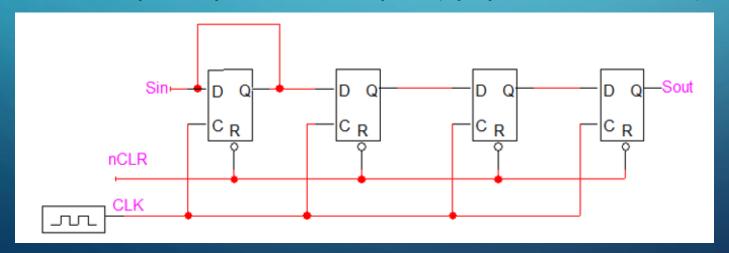

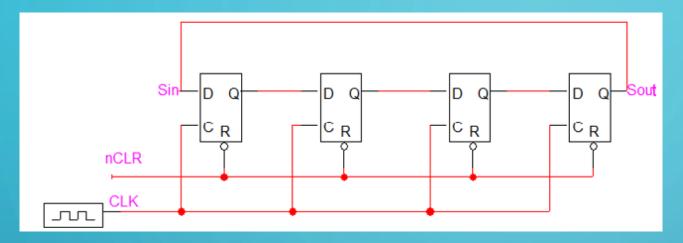

# РЕГИСТР СО СДВИГОМ ВПРАВО

## 4-битный регистр со сдвигом вправо (логический сдвиг)

### 4-битный регистр со сдвигом вправо (арифметический сдвиг)

## 4-битный регистр со сдвигом вправо (циклический сдвиг)

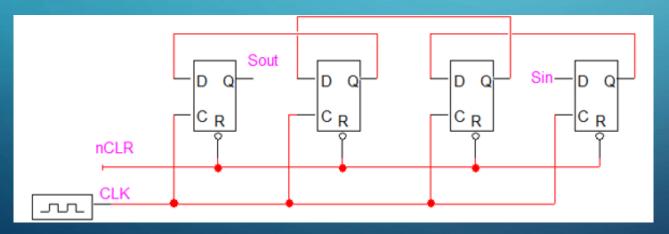

## 4-битный регистр со сдвигом влево (логический сдвиг)

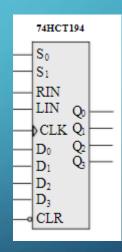

# <sup>©</sup> РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА

## ПРИМЕНЕНИЯ РЕГИСТРОВ

Преобразование последовательного двоичного слова в параллельное

Преобразование параллельного двоичного слова в последовательное

### Кольцевой счетчик

Основное применение - последовательная генерация управляющих сигналов, предназначенных для последовательного переключения *п* цифровых схем. Счетчик использует комбинированный регистр с параллельной загрузкой и чтением (PIPO), снабженный последовательным вводом и выводом. При параллельной загрузке регистр (кольцевой счетчик) всегда инициализируется двоичным словом из *п* битов, на одном бите записывается логическая единица, на остальных – О. Параллельные выходы необходимы для получения управляющих сигналов без необходимости в декодере.

# СЧЕТЧИК JOHNSON

| Nr. tact     | Q3 | Q2 | Q1 | Q0 |

|--------------|----|----|----|----|

| Inițializare | 0  | 0  | 0  | 0  |

| 1            | 0  | 0  | 0  | 1  |

| 2            | 0  | 0  | 1  | 1  |

| 3            | 0  | 1  | 1  | 1  |

| 4            | 1  | 1  | 1  | 1  |

| 5            | 1  | 1  | 1  | 0  |

| 6            | 1  | 1  | 0  | 0  |

| 7            | 1  | 0  | 0  | 0  |

| 8            | 0  | 0  | 0  | 0  |

| 9            | 0  | 0  | 0  | 1  |

| 10           | 0  | 0  | 1  | 1  |

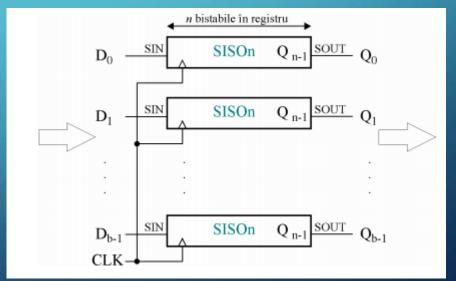

#### Память FIFO и LIFO

Они представляют собой временную память, организованную как n двоичные слова по m бит каждое, состоящих из m регистров последовательного сдвига SISO по n бит каждый.

FIFO – First In First Out (первое написанное слово - первое прочитанное).

LIFO - Last In First Out (последнее написанное слово - первое прочитанное).

# СИНТЕЗ РЕГИСТРОВ

Для выбора режима функционирования используются управляющие сигналы

Количество управляющих сигналов n зависит от количества рабочих режимов, и определяется согласно формуле  $n = \log 2m$  [.

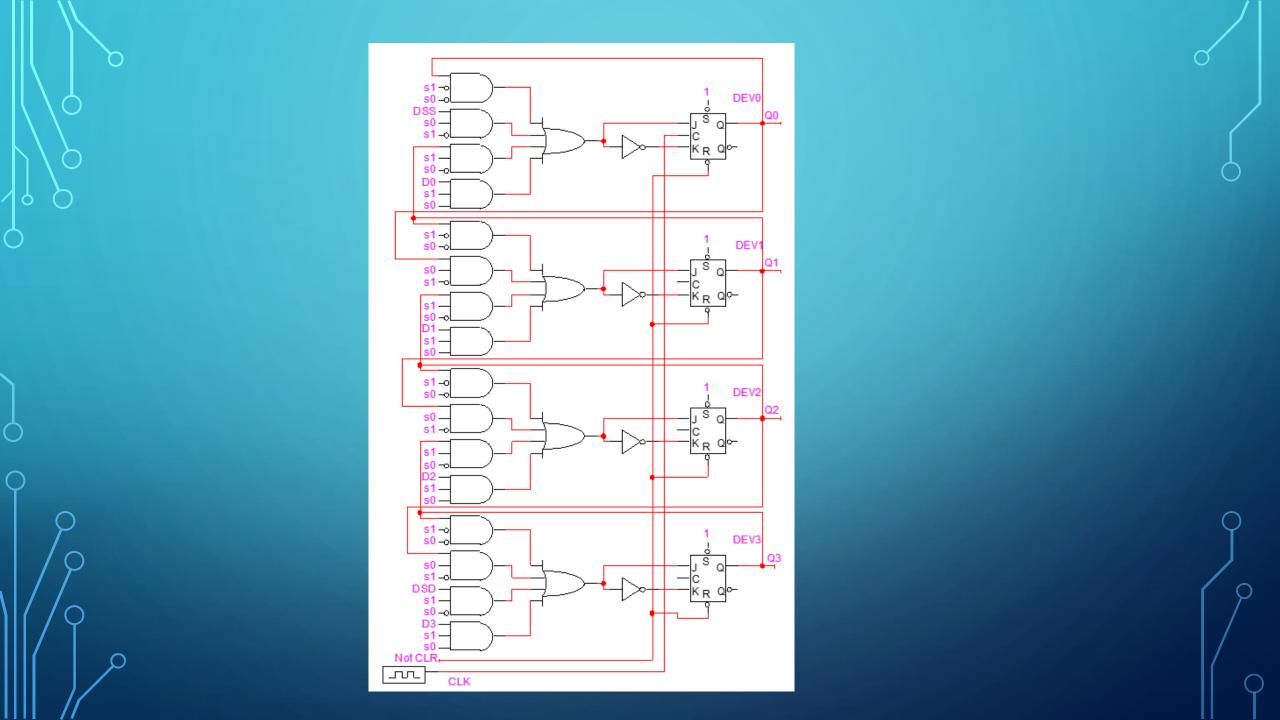

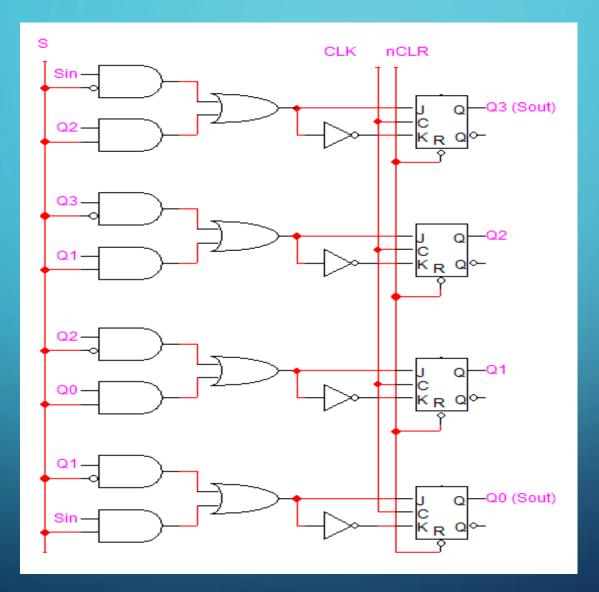

Выполнить синтез 4-разрядного регистра который имеет следующие режимы работы:

- 1. Хранение

- 2. Логический сдвиг влево

- 3. Логический сдвиг вправо

- 4. Параллельная загрузка

Используем 2 управляющих сигнала s1 и s0

Таблица переходов для универсального регистра:

| Режим работы          | Сигналы    |    | Выходы |         |         |         |      |  |

|-----------------------|------------|----|--------|---------|---------|---------|------|--|

|                       | управления |    |        |         |         |         |      |  |

|                       | S1         | S0 | Q3     | Q2      | Q1      | Q0      | t    |  |

| Сохранение            | 0          | 0  | $Q_3$  | $Q_2$   | $Q_{l}$ | Q0      | 41.1 |  |

| Сдвиг влево           | 0          | 1  | $Q_2$  | $Q_{l}$ | Q0      | DSS     | t+1  |  |

| Сдвиг вправо          | 1          | 0  | DSD    | $Q_3$   | $Q_2$   | $Q_{l}$ |      |  |

| Параллельная загрузка | 1          | 1  | $D_3$  | $D_2$   | $D_l$   | $D_0$   |      |  |

### Логические формулы:

$$\begin{split} J_3 &= \overline{K}_3 = \overline{s}_1 \overline{s}_0 Q_3 \vee \overline{s}_1 s_0 Q_2 \vee s_1 \overline{s}_0 DSD \vee s_1 s_0 D_3, \\ J_2 &= \overline{K}_2 = \overline{s}_1 \overline{s}_0 Q_2 \vee \overline{s}_1 s_0 Q_1 \vee s_1 \overline{s}_0 Q_3 \vee s_1 s_0 D_2, \\ J_1 &= \overline{K}_1 = \overline{s}_1 \overline{s}_0 Q_1 \vee \overline{s}_1 s_0 Q_0 \vee s_1 \overline{s}_0 Q_2 \vee s_1 s_0 D_1, \\ J_0 &= \overline{K}_0 = \overline{s}_1 \overline{s}_0 Q_0 \vee \overline{s}_1 s_0 DSS \vee s_1 \overline{s}_0 Q_1 \vee s_1 s_0 D_0. \end{split}$$