# VII. СИНТЕЗ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ

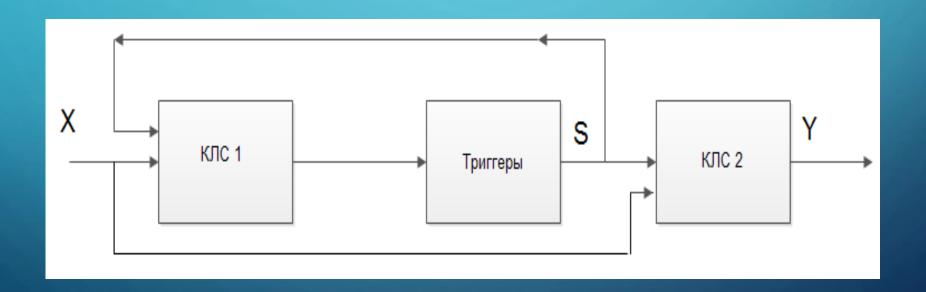

Текущее состояние последовательностных логических схем (ПЛС) определяется не только поступившими входными сигналами, но и предыдущими значениями входных сигналов.

ПЛС содержит конечное число элементов памяти и управляющую комбинационную логическую схему.

Состояние ПЛС определяется общим состоянием всех триггеров. ПЛС с *п* триггерами может иметь до **2**<sup>n</sup> состояний.

По режиму работы различают 2 основные категории ПЛС:

- 1. асинхронные ПЛС

- 2. синхронные ПЛС

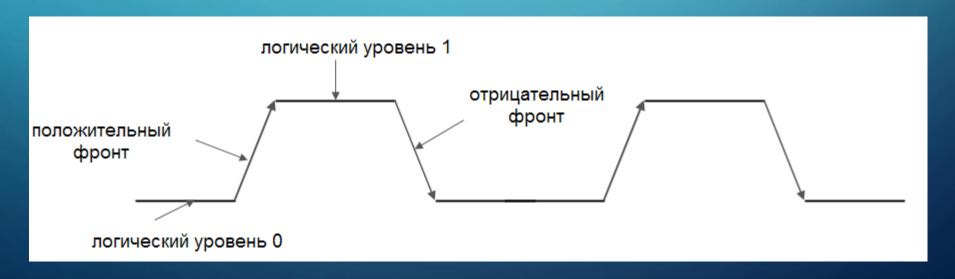

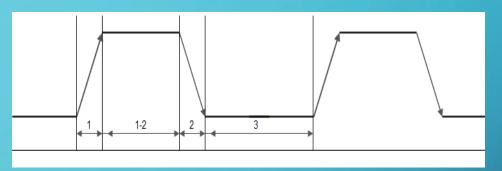

Временная диаграмма тактового сигнала:

#### ЭТАПЫ СИНТЕЗА ПЛС

- 1. Описание функционирования

- 2. Таблица переходов между состояниями, которая включает входные переменные в момент времени t, значения выходных функций в момент времени t + 1.

- 3. Минимизация логических функций

- 4. Реализация схемы.

#### **ТЕМА 7.1** ТРИГГЕРЫ

Триггеры) - это последовательностные логические схемы, которые имеют два различных стабильных состояния 0 и 1.

В зависимости от режима переключения триггеры подразделяются на:

Latch (одноуровневые триггеры, которые переключаются при *погическом уровене* 0 или логическом уровене 1 тактового сигнала).

**Flip-flop** (двухуровневые триггеры, ведущий-ведомый (master-slave), которые переключаются при **положительном или отрицательном фронте** тактового сигнала).

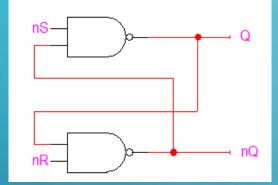

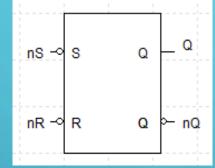

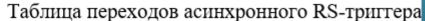

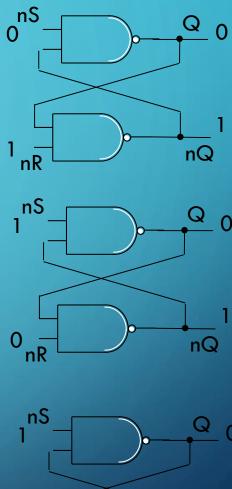

# АСИНХРОННЫЙ RS ТРИГГЕР (LATCH)

• S (Set)

• R (Reset)

Логическая схема триггера получается путем соединения линиями обратной связи двух инвертирующих логических элементов. Сигналы R и S активны по O (обратная логика)

| St | R <sub>t</sub> | Q <sub>t+1</sub> | nQ <sub>t+1</sub> | Комментарии                      |

|----|----------------|------------------|-------------------|----------------------------------|

| 0  | 0              | -                | -                 | Запрещенное состояние            |

| 0  | 1              | 1                | 0                 | Установка в 1 Set                |

| 1  | 0              | 0                | 1                 | Установка в 0 Reset              |

| 1  | 1              | Qt               | nQt               | Сохранение предыдущего состояния |

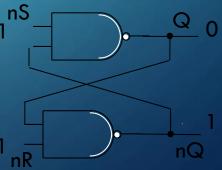

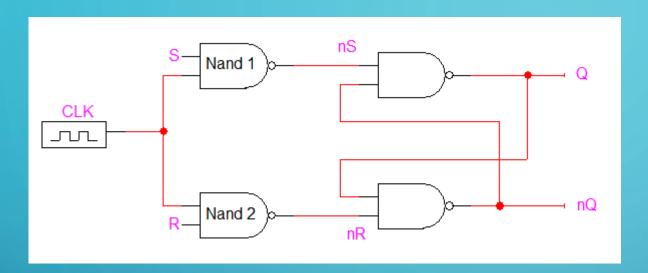

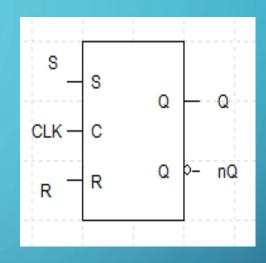

# СИНХРОННЫЙ RS ТРИГГЕР (LATCH)

| Таблица переходов синхронного RS-триг |                |           |                   |                                  |  |  |

|---------------------------------------|----------------|-----------|-------------------|----------------------------------|--|--|

| St                                    | R <sub>t</sub> | $Q_{t+1}$ | nQ <sub>t+1</sub> | Комментарии                      |  |  |

| 0                                     | 0              | Qt        | nQt               | Сохранение предыдущего состояния |  |  |

| 0                                     | 1              | 0         | 1                 | Установка в 0 Reset              |  |  |

| 1                                     | 0              | 1         | 0                 | Установка в 1 Set                |  |  |

| 1                                     | 1              | -         | -                 | Запрещенное состояние            |  |  |

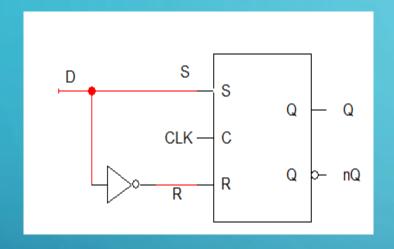

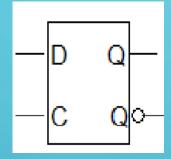

## СИНХРОННЫЙ D ТРИГГЕР (LATCH)

D (delay)

D триггер задерживает на один такт информацию, которую он получает на входе.

| ]                |           |                   |               | Таблица переход | ов D тригтера |

|------------------|-----------|-------------------|---------------|-----------------|---------------|

| $D_t$            | $Q_{t+1}$ | nQ <sub>t+1</sub> | Комментарии   |                 |               |

| 0                | 0         | 1                 | Установка в 0 |                 |               |

| 1                | 1         | 0                 | Установка в 1 |                 |               |

| N. E. A. William |           |                   |               |                 |               |

Основное назначение D триггера — хранение двоичных слов. Используется в регистрах и схемах RAM памяти

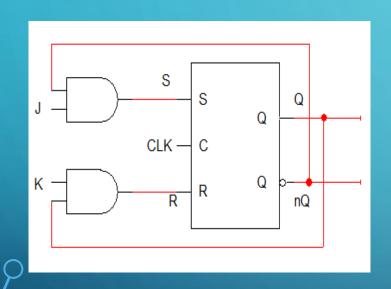

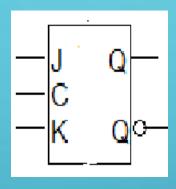

## СИНХРОННЫЙ ЈК ТРИГГЕР (LATCH)

JK триггер сохраняет свою функциональность и тогда, когда RS=1. Это достигается путем дополнительных линий обратной связи.

|       |           |                   | Таблица переходов ЈК т                  | ригтера |

|-------|-----------|-------------------|-----------------------------------------|---------|

| $K_t$ | $Q_{t+1}$ | nQ <sub>t+1</sub> | Комментарии                             |         |

| 0     | Qt        | nQt               | Сохранение предыдущего состояния        |         |

| 1     | 0         | 1                 | Установка в 0 Reset                     |         |

| 0     | 1         | 0                 | Установка в 1 Set                       |         |

| 1     | nQt       | Qt                | Инвертирование состояния Q <sub>t</sub> |         |

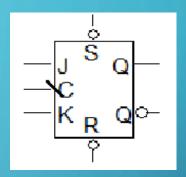

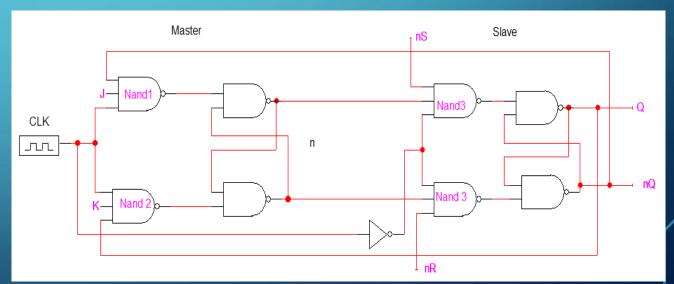

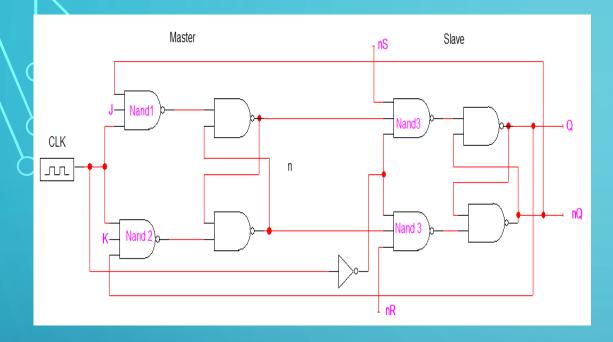

#### СИНХРОННЫЙ ЈК ТРИГГЕР (FLIP-FLOP)

Линия обратной связи приводит к тому что ЈК триггер

осциллирует когда J = K = 1

Flip-flop триггер решает эту проблему.

Структура flip-flop master-slave состоит из двух latch триггеров, одного "master" и другого "slave".

В flip-flop триггерах на положительном фронте тактового сигнала информация входит в ведущий триггер, при этом ведомый триггер практически отключен. На следующем отрицательном фронте информация передается от ведущего к ведомому триггеру, и появляется на выходах на отрицательном фронте тактового сигнала.

Входы nS и nR являются асинхронными входами, которые действуют на последнем уровне логических вентилей, не зависят от тактового сигнала и имеют приоритет над синхронными входами J и K (когда один из них активирован, триггер будет работать асинхронно).

Период времени 2 - это время установки т.е. период, в течение которого данные должны быть подготовлены до подачи тактового импульса. Период времени 3 - время паузы.

В течение периода времени 1 входные вентили еще не открыты, а вентили Nand3 и Nand4 блокируются и, таким образом, изолируют ведущий триггер от ведомого.

В зоне 1–2 элементы Nand1 и Nand2 открыты, и информация передается мастеру. Вентили Nand 3 и Nand 4 закрыты, и ведомый триггер хранит свою старую информацию.

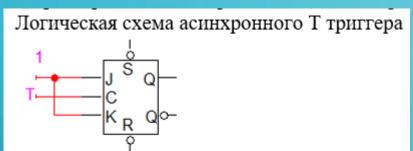

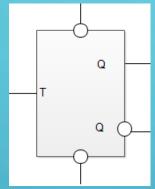

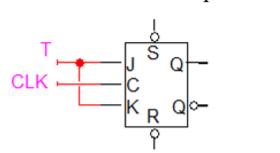

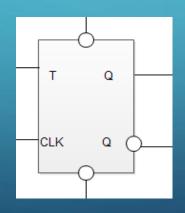

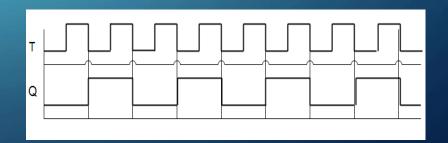

#### T ТРИГГЕР (FLIP-FLOP)

T триггер (Toggle) получается из JK триггера типа flip-flop при соединении входов J и K.

| T <sub>t</sub> | Q <sub>t+1</sub> | nQ <sub>t+1</sub> | Комментарии                      |

|----------------|------------------|-------------------|----------------------------------|

| 0              | Qt               | nQt               | Сохранение предыдущего состояния |

| 1              | nQt              | Qt                | Инвертирование состояния Qt      |

Логическая схема синхронного Т триггера

Триггер Т используется в счетчиках и в схемах деления частоты на 2.

### ТАБЛИЦЫ ВОЗБУЖДЕНИЯ ТРИГГЕРОВ.

| St | R <sub>t</sub> | Q <sub>t+1</sub> | nQ <sub>t+1</sub> |

|----|----------------|------------------|-------------------|

| 0  | 0              | Qt               | nQt               |

| 0  | 1              | 0                | 1                 |

| 1  | 0              | 1                | 0                 |

| 1  | 1              | -                | -                 |

| Qt | Q <sub>t+1</sub> | S | R |

|----|------------------|---|---|

| 0  | 0                |   |   |

| 0  | 1                |   |   |

| 1  | 0                |   |   |

| 1  | 1                |   |   |

| T <sub>t</sub> | $Q_{t+1}$ | nQ <sub>t+1</sub> |

|----------------|-----------|-------------------|

| 0              | Qt        | $nQ_t$            |

| 1              | nQt       | Qt                |

| Qt | Q <sub>t+1</sub> | T |

|----|------------------|---|

| 0  | 0                |   |

| 0  | 1                |   |

| 1  | 0                |   |

| 1  | 1                |   |

| D <sub>t</sub> | $Q_{t+1}$ | nQ <sub>t+1</sub> |

|----------------|-----------|-------------------|

| 0              | 0         | 1                 |

| 1              | 1         | 0                 |

| Qt | Q <sub>t+1</sub> | D |

|----|------------------|---|

| 0  | 0                |   |

| 0  | 1                |   |

| 1  | 0                |   |

| 1  | 1                |   |

| $J_{t}$ | $K_t$ | $Q_{t+1}$ | $nQ_{t+1}$ |

|---------|-------|-----------|------------|

| 0       | 0     | Qt        | $nQ_t$     |

| 0       | 1     | 0         | 1          |

| 1       | 0     | 1         | 0          |

| 1       | 1     | nQt       | Qt         |

| Qt | $Q_{t+1}$ | J | K |

|----|-----------|---|---|

| 0  | 0         |   |   |

| 0  | 1         |   |   |

| 1  | 0         |   |   |

| 1  | 1         |   |   |