# VI. ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ СХЕМ

**ТЕМА 6.4. СУММАТОРЫ**

### СУММАТОРЫ

Сумматоры выполняют операцию сложения двух чисел и операцию вычитания, которая заключается в суммировании вычитаемого с дополнительным кодом вычитателя.

Структура всех сумматоров основывается на двух логических схем суммирования, известных как:

полусумматор (Half sum, обозначенная HS) и

полный сумматор (Full sum, обозначенная SM)

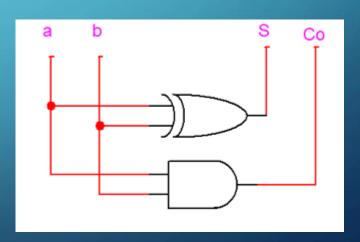

### ПОЛУСУММАТОР

Полусумматор - это КЛС, который складывает 2 бита без учета переноса из предыдущего разряда. На выходе формируется Сумма (S) и Перенос в следующий разряд (Co).

| a | b | S | C <sub>0</sub> |

|---|---|---|----------------|

| 0 | 0 | 0 | 0              |

| 0 | 1 | 1 | 0              |

| 1 | 0 | 1 | 0              |

| 1 | 1 | 0 | 1              |

$$S = a \oplus b$$

$$C_0 = ab$$

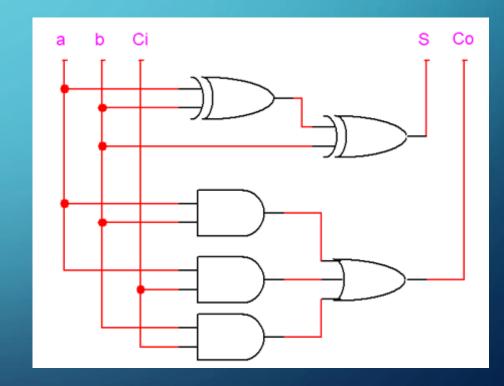

## ПОЛНЫЙ СУММАТОР

**Полный сумматор** - это КЛС, который складывает 2 бита и перенос Сі из предыдущего разряда. На выходе полный сумматор формирует Сумму

(S) и Перенос в следующий разряд (Co).

| a | b | Ci | S | $C_0$ |

|---|---|----|---|-------|

| 0 | 0 | 0  | 0 | 0     |

| 0 | 0 | 1  | 1 | 0     |

| 0 | 1 | 0  | 1 | 0     |

| 0 | 1 | 1  | 0 | 1     |

| 1 | 0 | 0  | 1 | 0     |

| 1 | 0 | 1  | 0 | 1     |

| 1 | 1 | 0  | 0 | 1     |

| 1 | 1 | 1  | 1 | 1     |

| x3 00 01 11 10<br>0 1 1 | x1x2 |    |    |    |    |

|-------------------------|------|----|----|----|----|

| 0 1 1                   | x3   | 00 | 01 | 11 | 10 |

|                         | 0    |    | 1  |    | 1  |

| 1 1   1                 | 1    | 1  |    | 1  |    |

|   | x1x2 |    |    |    |    |

|---|------|----|----|----|----|

|   | х3   | 00 | 01 | 11 | 10 |

|   | 0    |    |    | 1  |    |

| 1 | 1    |    | 1  |    | 1  |

|   |      |    |    |    |    |

$$S = a \oplus b \oplus C_{i}$$

$$C_{0} = ab + aC_{i} + bC_{i}$$

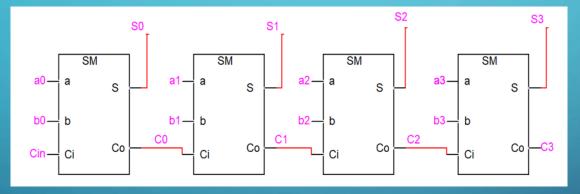

## ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР

Сумматоры для сложения n-разрядных двоичных слов реализуются путем соединения 1-разрядных сумматоров.

В этой схеме сложение выполняется параллельно, и распространение переноса происходит последовательно, что приводит к суммированию времени задержки, так что конечный результат обеспечивается с довольно большой задержкой по сравнению с входным сигналом.

$A=a_3a_2a_1a_0$  $B=b_3b_2b_1b_0$

**Преимущество** последовательного сумматора - невысокая стоимость. **Недостатком** является то, что время задержки увеличивается пропорционально количеству разрядов.

### СУММАТОР С УСКОРЕННЫМ ПЕРЕНОСОМ

Решение в этом случае является архитектурным и предполагает отказ от последовательного переноса в пользу параллельного (ускоренного). Фактически это означает переопределение логической функции, которая формирует сигнал переноса.

$$c_{i+1} = a_i b_i \vee a_i c_i \vee b_i c_i = a_i b_i \vee (a_i \vee b_i) c_i.$$

Определим 2 функции: G – Функция генерации переноса  $G_i = a_i b_i$

P – функция передачи переноса  $P_i = a_i \lor b_i$

$$P_i = a_i \vee b_i$$

В этом случае, формулу для переноса можно записать следующим образом:

$$c_{i+1} = G_i \vee P_i c_i$$

$$\begin{split} c_1 &= G_0 \vee P_0 c_{IN} \,; \\ c_2 &= G_1 \vee P_1 c_1 = G_1 \vee P_1 (G_0 \vee P_0 c_{IN}) = G_1 \vee P_1 G_0 \vee P_1 P_0 c_{IN} \,; \\ c_3 &= G_2 \vee P_2 c_2 = G_2 \vee P_2 (G_1 \vee P_1 G_0 \vee P_1 P_0 c_{IN}) = G_2 \vee P_2 G_1 \vee P_2 P_1 G_0 \vee P_2 P_1 P_0 c_{IN} \end{split}$$

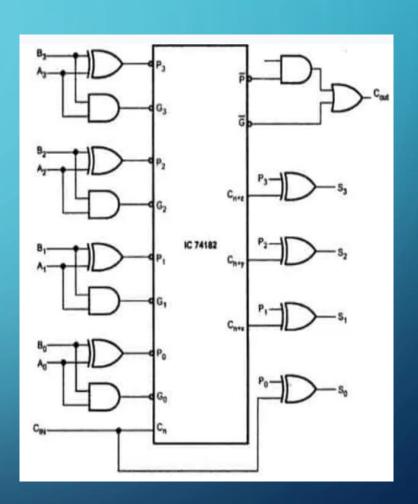

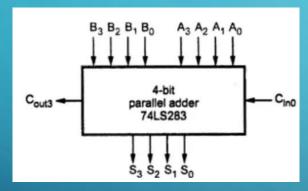

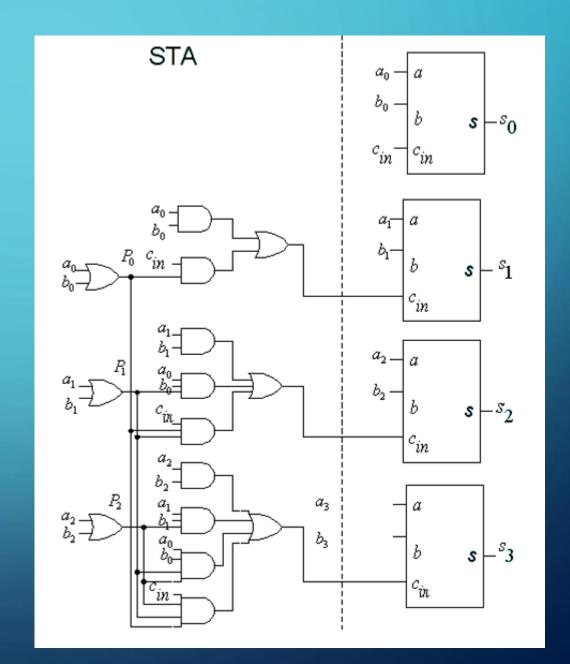

Схема 4х разрядного сумматора с ускоренным переносом:

В состав сумматора с ускоренным переносом входят два модуля:

- модуль суммирования, состоящий из нескольких одноразрядных сумматоров

- модуль для формирования ускоренного переноса.

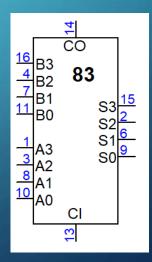

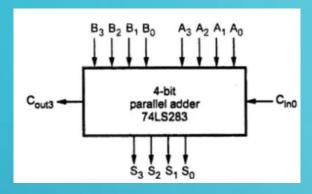

Интегральная схема 4-битного сумматора с ускоренным переносом 74\_283:

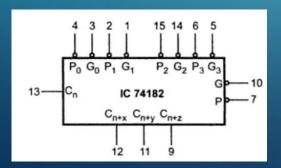

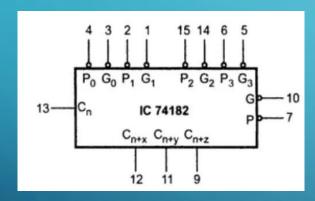

Микросхема генерации переноса 74\_182:

#### Преимущества сумматора с ускоренным переносом

- 1. Перенос генерируется для каждого сумматора одновременно с использованием упрощенных уравнений, включающих Рі, Gi и Cin.

- 2. Эта схема уменьшает задержку распространения. Это связано с тем, что выходной перенос зависит только от первого сигнала переноса, подаваемого на вход.

- 3. Это самый быстрый сумматор по сравнению с другими типами сумматоров.

#### Недостатки

- 1. Схема сумматора с ускоренным переносом усложняется с увеличением числа разрядов.

- 2. Схема сумматора с ускоренным переносом стоит дорого, поскольку требует большего количества оборудования.

- 3. По мере увеличения числа переменных интегральная схема содержит больше логических вентилей, поэтому площадь этой схемы увеличивается.

Интегральная схема 4-битного сумматора с ускоренным переносом 74\_283:

Микросхема генерации переноса 74\_182:

$$C_{n+x} = G0 + P0$$

. Cn

$C_{n+y} = G1 + P1$ .  $G0 + P1$ .  $P0$ . Cn

$C_{n+z} = G2 + P2$ .  $G1 + P2$ .  $P1$ .  $G0$

$G' = (G3 + P3$ .  $G2 + P3$ .  $P2$ .  $G1 + P3$ .  $P2$ .  $P1$ .  $G0$ .)'

$P' = (P3$ .  $P2$ .  $P1$ .  $P0$ .)'