## Тема 6.3. Преобразователи кодов

В принципе любое цифровое устройство преобразует некоторый входной код в некоторый выходной, т. е. является кодовым преобразователем. Однако по традиции к преобразователям кодов относят устройства, которые изменяют вид кодирования данных.

Рассмотрим кратко вопрос реализации двух видов преобразований.

Как известно, двоичные числа могут быть представлены в прямом, обратном или дополнительном кодах.

Преобразователи прямого кода в обратный

$$\begin{array}{ccc} X_{cd}\!\!=\!\!01010 & Y_{cd}\!\!=\!\!11010 \\ X_{ci}\!\!=\!\!01010 & Y_{ci}\!\!=\!\!10101 \end{array}$$

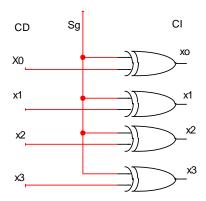

$$[x_i]_{ci} = [x_i]_{cd} \oplus Sg$$

Преобразование прямого кода в обратный реализуется сложением по модулю 2 значений кода данного разряда и сигнала управления преобразователем. При этом нулевое значение сигнала управления обеспечивает прохождение на выход устройства прямого кода числа. При единичном значении сигнала управления каждый разряд выходного кода будет инверсией соответствующего разряда входного кода. Очевидно, в качестве сигнала управления преобразователем прямого кода в обратный может быть непосредственно использовано значение знакового разряда.

Преобразователи прямого кода в дополнительный

$$X_{cd}$$

=01100  $Y_{cd}$ =11100  $Y_{ci}$ =10100  $Y_{ci}$ =10100

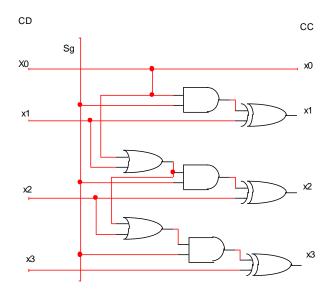

Преобразование прямого кода в дополнительный реализуется сложнее. В этом случае операция преобразования не является поразрядной, и для определения значения кода в каком-либо разряде требуется анализ значений других разрядов. Известно, что для получения дополнительного кода нужно проинвертировать все разряды преобразуемого кода и затем прибавить к результату 1.

Сопоставление прямого и дополнительного кодов показывает, что последний отличается от первого инвертированием старших разрядов от n-1 до i+1 включительно, где i — номер первого справа разряда, содержащего 1. Остальные разряды остаются неизменными. Например, для прямого кода 10011010 дополнительным будет код 01100110. Аналитически это правило записывается в виде выражения

$$[x_i]_{cc} = [x_i]_{cd} \oplus \{(x_{i-1} + x_{i-2} + ... + x_0) \cdot Sg\}$$

согласно которому для получения i-го разряда дополнительного кода необходимо сложить по модулю 2 исходный код этого разряда с дизьюнкцией всех предыдущих (младших) разрядов.

Знаковый разряд преобразуемого кода можно использовать в качестве управляющего сигнала.

## Двоично-десятичные преобразователи

Выполнить синтез двоично-десятичные преобразователя 8 7  $\,$  (-2) (-7)  $\rightarrow$  4 2 2 1

Таблица истинности:

| nerminoern. |            |       |    |    |         |       |       |       |

|-------------|------------|-------|----|----|---------|-------|-------|-------|

|             | 87(-2)(-4) |       |    |    | 4221    |       |       |       |

| Nr.         | $x_1$      | $x_2$ | Х3 | X4 | $f_{I}$ | $f_2$ | $f_3$ | $f_4$ |

| 0           | 0          | 0     | 0  | 0  | 0       | 0     | 0     | 0     |

| 1           | 0          | 1     | 1  | 1  | 0       | 0     | 0     | 1     |

| 2           | 1          | 0     | 1  | 1  | 0       | 0     | 1     | 0     |

| 3           | 0          | 1     | 0  | 1  | 0       | 0     | 1     | 1     |

| 4           | 1          | 0     | 0  | 1  | 0       | 1     | 1     | 0     |

| 5           | 0          | 1     | 1  | 0  | 1       | 0     | 0     | 1     |

| 6           | 1          | 0     | 1  | 0  | 1       | 1     | 0     | 0     |

| 7           | 0          | 1     | 0  | 0  | 1       | 1     | 0     | 1     |

| 8           | 1          | 0     | 0  | 0  | 1       | 1     | 1     | 0     |

| 9           | 1          | 1     | 1  | 1  | 1       | 1     | 1     | 1     |

| 10          | 0          | 0     | 0  | 1  | *       | *     | *     | *     |

| 11          | 0          | 0     | 1  | 0  | *       | *     | *     | *     |

| 12          | 0          | 0     | 1  | 1  | *       | *     | *     | *     |

| 13          | 1          | 1     | 0  | 0  | *       | *     | *     | *     |

| 14          | 1          | 1     | 0  | 1  | *       | *     | *     | *     |

| 15          | 1          | 1     | 1  | 0  | *       | *     | *     | *     |

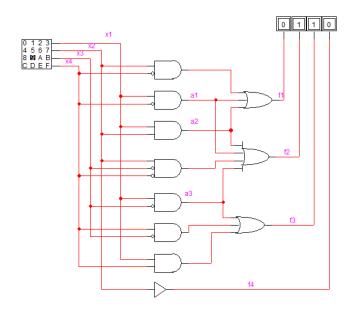

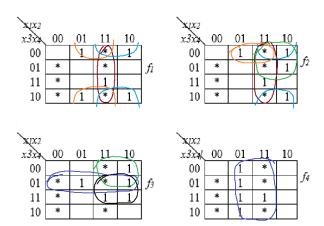

В результате минимизации были получены следующие логические функции:  $f_1=x_1\overline{x}_4\vee x_2\overline{x}_4\vee x_1x_2;$

$$\begin{split} f_1 &= x_1 \bar{x}_4 \vee x_2 \bar{x}_4 \vee x_1 x_2; \\ f_2 &= x_2 \bar{x}_3 \bar{x}_4 \vee x_1 \bar{x}_4 \vee x_1 x_2 + x_1 \bar{x}_3; \\ f_3 &= x_1 \bar{x}_3 \vee \bar{x}_3 x_4 \vee x_1 x_4; \\ f_4 &= x_2. \end{split}$$

Определяем общие термины:

$$a_1 = x_1 \overline{x}_4;$$

$$a_2 = x_1 x_2$$

$$a_3 = x_1 \overline{x}_3$$

С учетом общих терминов функции  $f_1, f_2, f_3, f_4$  можно записать следующим образом:  $f_1 = a_1 \vee a_2 \vee x_2 \overline{x}_4;$

$$\begin{split} f_1 &= a_1 \lor a_2 \lor x_2 x_4; \\ f_2 &= a_1 \lor a_2 \lor a_3 \lor x_2 \overline{x}_3 \overline{x}_4; \\ f_3 &= a_3 \lor \overline{x}_3 x_4 \lor x_1 x_4; \\ f_4 &= x_2. \end{split}$$

Схема преобразователя 8 7 (-2) (-4)  $\rightarrow$  4 2 2 1: